#### ALMA Memo 337

#### Development of Frequency Multiplier Technology for ALMA Kamaljeet S. Saini

This ALMA memo, also published as a dissertation at the University of Virginia in January 2003 (UVA Science Engineering Library call number Diss. Engr. 2003.S24), presents a novel GaAs on Quartz based approach toward larger band-width Schottky diode frequency multipliers and reports the first fully integrable frequency multiplier based on this composite substrate is reported. This technology was developed as a low cost solution for meeting the ALMA frequency multiplier requirement up to about 400 GHz.

This technology has since then been commercially applied to design and build frequency triplers for the first local oscillator chains for ALMA bands 6 and 7.

The memo also describes other contemporary state-of-the-art frequency multiplier technologies and provides a comprehensive up to date survey of existing frequency multiplier designs together with their measured performances from published literature.

## Abstract

A key requirement for the operation of a super-heterodyne millimeter- and submillimeter- wave receiver is the availability of a local oscillator (LO) signal used to pump a non-linear component such as a low noise superconductorinsulator-superconductor (SIS) junction, a Schottky-diode, or a Hot Electron Bolometer (HEB) device that down-converts the received Radio Frequency (RF) signal. Frequency multipliers have been used for many years to produce the required LO power. Traditionally, these frequency multipliers have been "hybrid" circuits, designed around planar discrete diode array packages fabricated on tiny pieces of semiconductor (GaAs, InP) material. The diode packages are attached to embedding circuitry usually fabricated on a low dielectric material like quartz. This approach, while highly successful up to about 100 GHz, has inherent drawbacks (of process, parasitic and performance variabilities, as well as being labor intensive) that limits its applicability for higher frequencies.

This dissertation describes the design, fabrication and evaluation of three frequency multipliers: The 55/110 GHz and the 110/220 GHz frequency doublers and the 80/240 GHz frequency tripler. The frequency doublers were designed based on the hybrid-circuit approach and illustrate the limitations of extending this approach to design frequency multipliers for frequencies above 100 GHz. The 80/240 GHz frequency tripler was designed to be fully integrable and used diode chips that were fabricated on a composite substrate comprising of GaAs-membrane-on-quartz, suitable for the fabrication of linear embedding circuitry alongside the diodes on the same chip. This is the first reported frequency multiplier to 1) use the UVA GaAs-membrane-onquartz process to implement balanced diode configuration with an integrated and optimized idler loop, 2) innovatively use an air-gap in the microstrip transmission line to synthesize a high-quality series negative reactance tuning element, and 3) use 1 mil thick fused-quartz substrate for linear embedding circuitry. This approach circumvents the "dielectric loading" problems of GaAs-based MMIC multipliers as well as the fragile nature of the rather large thinned-substrate or membrane type MMICs that are more suited to applications beyond 300 GHz.

The first experimental study of planar capacitor and spiral inductors, to gauge their applicability for high frequency multiplier MMIC work, was also a part of this research. The final part of the research focused on analytical and simulation based study to characterize the sideband noise transmission characteristics of diode based frequency multipliers. These noise characteristics are important, particularly in cases where the un-filtered output of a frequency multiplier is used to pump a frequency converter having a large IF bandwidth (often the case in millimeter- and submillimeter- wave receivers).

## Acknowledgments

I would like to recognize the support of the sponsor for this research, National Radio Astronomy Observatory (NRAO), Charlottesville, and the technical support from members of the UVA Semiconductor Device Laboratory (SDL), UVA Far-Infrared Laboratory (FIR-Lab.), as well as the Central Development Laboratory (CDL) at NRAO, Charlottesville.

I especially wish to thank my advisor Dr. Richard F. Bradley for all his guidance and patience during the course of this research as well as preparation of this dissertation. I also wish to thank Dr. Thomas W. Crowe for the numerous technical discussions and all the helpful suggestions during the course of my MMIC work.

This work could not have been accomplished without the help and support of everybody around me. I am thankful to Gerhard S. Schoenthal (SDL) and to Manjunath S. Bhat (SDL) for fabricating all the various devices and structures needed during the course of this research. I thank Donald G. Stone (CDL) for the drafting work required to fabricate the mask-sets and machine the various frequency multiplier blocks. For machining of the various metal blocks, I thank Dylon Dillon (CDL) and Anthony Marshall (CDL). I thank Patrick Madigan (NRAO, Soccorro) for machining the mandrels for the 110/220 GHz block and Vincent Summers (CDL) for performing the electro-deposition. I wish to acknowledge my appreciation to Michael J. Stogoski (CDL) for his help with developing the process for and fabricating all the various quartz circuits used during the course of this work. I also thank Francoise Johnson (CDL) for her precision dicing work. I am thankful to Anthony R. Kerr (CDL), S. K. Pan (CDL), Marian Pospiezalski (CDL), Gerry Petencin (CDL), David W. Porterfield (FIR-Lab.), and Jeffrey L. Hesler (FIR-Lab.) for technical discussions and invaluable insights at various stages during the course of my research.

I wish to extend a special note of thanks to the entire staff at NRAO for their generosity with both time and equipment.

Finally, I extend my warmest appreciation and gratitude to my wife, Harnavleen, who put up with many long hours during this research. Her patience, encouragement and support saw me through the difficult times of my research.

## Contents

| 1 | Intr | roduction                                                    | 1         |

|---|------|--------------------------------------------------------------|-----------|

|   | 1.1  | Background and Motivation                                    | 2         |

|   | 1.2  | Fundamental Millimeter- and Submillimeter-wave Oscillators . | 4         |

|   |      | 1.2.1 Vacuum and Gas-filled Tube Sources                     | 5         |

|   |      | 1.2.2 Solid-state Sources                                    | 6         |

|   | 1.3  | Millimeter- and Submillimeter-wave Generation by Photonic    |           |

|   |      | Mixing and Detection                                         | 10        |

|   | 1.4  | Millimeter- and Submillimeter-wave Frequency Multipliers     | 12        |

|   | 1.5  | Research Objectives                                          | 18        |

| 2 | Hyb  | orid-MIC Frequency Doublers                                  | <b>21</b> |

|   | 2.1  | Introduction                                                 | 22        |

|   | 2.2  | Balanced Frequency Doubler Configuration                     | 24        |

|   | 2.3  | Operation of the Doubler Circuit                             | 26        |

|   | 2.4  | Planar Schottky Varactor Design                              | 28        |

|   |      | 2.4.1 Review of the Schottky Varactor Theory                 | 28        |

|   |      |                                                              | 36        |

|   |      | 2.4.2 Determination of Primary Design Parameters             |           |

|   |      |                                                              | 40        |

3

|      | 2.5.1   | HP High Frequency Structure Simulator (HP-HFSS) .    | 43 |

|------|---------|------------------------------------------------------|----|

|      | 2.5.2   | Design of the Input Section                          | 48 |

|      | 2.5.3   | Design of the Output Section                         | 51 |

|      | 2.5.4   | Design of the DC Bias Filter                         | 53 |

|      | 2.5.5   | Design of the Output Waveguide Taper                 | 54 |

|      | 2.5.6   | Design of the Output Microstrip to Waveguide Coupler | 55 |

| 2.6  | Fabric  | ation and Assembly                                   | 58 |

| 2.7  | Evalua  | ation                                                | 59 |

| 2.8  | The 1   | 10/220 GHz Frequency Doubler                         | 65 |

|      | 2.8.1   | Planar Schottky Varactor Design                      | 65 |

|      | 2.8.2   | Linear Embedding Circuit Design                      | 69 |

|      | 2.8.3   | Fabrication and Assembly                             | 69 |

|      | 2.8.4   | Evaluation                                           | 72 |

| 2.9  | Discus  | sion of Results                                      | 76 |

| 2.10 | Conclu  | lsion                                                | 78 |

| Mo   | nolithi | c Technology                                         | 81 |

| 3.1  | Introd  | uction                                               | 81 |

| 3.2  | Mater   | ial System and Substrate                             | 82 |

| 3.3  | Transı  | mission Line                                         | 86 |

| 3.4  | Waveg   | guide Transitions                                    | 87 |

| 3.5  | Integr  | ated Capacitors                                      | 90 |

|      | 3.5.1   | Test Devices                                         | 90 |

|      | 3.5.2   | Experimental Setup                                   | 91 |

|      | 3.5.3   | Test Procedure                                       | 92 |

|      | 3.5.4   | Measurement Results                                  | 94 |

|   |     | 3.5.5   | Conclusion                                                                                     | 5 |

|---|-----|---------|------------------------------------------------------------------------------------------------|---|

|   | 3.6 | Integra | ted Inductors                                                                                  | 3 |

|   |     | 3.6.1   | Test Structure and Experimental Setup                                                          | 7 |

|   |     | 3.6.2   | Results                                                                                        | 3 |

|   | 3.7 | Conclu  | $sion \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $                         | ) |

| 4 | A F | ully In | tegrable Frequency Tripler 101                                                                 | L |

|   | 4.1 | Introdu | $\mathbf{nction}$                                                                              | 2 |

|   | 4.2 | An Alt  | ernate Frequency Tripler Configuration 104                                                     | 1 |

|   | 4.3 | The 80  | /240 GHz Frequency Tripler                                                                     | 7 |

|   | 4.4 | Design  | of the Integrated Device                                                                       | ) |

|   |     | 4.4.1   | The DC Bias Bypass Capacitor                                                                   | ) |

|   |     | 4.4.2   | Determination of Primary Design Parameters 111                                                 | L |

|   |     | 4.4.3   | Design of the Planar Diode Chip                                                                | 5 |

|   | 4.5 | Linear  | Embedding Circuit Design                                                                       | 7 |

|   |     | 4.5.1   | Design of the Input Circuit                                                                    | ) |

|   |     | 4.5.2   | Design of the Output Circuit                                                                   | 3 |

|   |     | 4.5.3   | Harmonic Balance Simulations                                                                   | 1 |

|   | 4.6 | Fabrica | ation and Assembly                                                                             | 5 |

|   | 4.7 | Evalua  | tion                                                                                           | 3 |

|   | 4.8 | Redesig | gn of the $80/240$ GHz Frequency Tripler                                                       | L |

|   |     | 4.8.1   | Design of the Linear Embedding Circuit                                                         | L |

|   |     | 4.8.2   | Fabrication and Assembly                                                                       | 3 |

|   |     | 4.8.3   | Evaluation                                                                                     | 5 |

|   | 4.9 | Conclu  | $sion \ldots 147$ | 7 |

| 5 | Noi  | se Ana   | alysis                                                | 149                 |

|---|------|----------|-------------------------------------------------------|---------------------|

|   | 5.1  | Introd   | luction                                               | . 150               |

|   | 5.2  | Static   | Analysis of Noise Transmission                        | . 151               |

|   |      | 5.2.1    | Time Domain Description                               | . 152               |

|   |      | 5.2.2    | Noise Transmission Matrix                             | . 154               |

|   |      | 5.2.3    | Output Noise Densities                                | . 156               |

|   | 5.3  | Analys   | sis of Sideband Noise Conversion                      | . 158               |

|   |      | 5.3.1    | Noise Analysis by Linear Frequency Converter Techniqu | <mark>te</mark> 159 |

|   |      | 5.3.2    | Noise Analysis by Two-Tone Harmonic Balance Simu-     |                     |

|   |      |          | lations                                               | . 160               |

|   |      | 5.3.3    | Simulation Strategy                                   | . 161               |

|   |      | 5.3.4    | Circuit Configuration                                 | . 162               |

|   |      | 5.3.5    | Simulation Results                                    | . 164               |

|   | 5.4  | Conclu   | usion                                                 | . 165               |

| 6 | Cor  | clusio   | ns                                                    | 167                 |

|   | 6.1  | Overv    | iew                                                   | . 168               |

|   | 6.2  | Sugges   | stions for Further Research                           | . 170               |

| A | Lite | erature  | e Review: Millimeter- and Submillimeter-wave Fre      | <b>)-</b>           |

|   | que  | ncy M    | ultipliers                                            | 172                 |

|   | A.1  | Abrup    | ot-junction Schottky diode                            | . 174               |

|   | A.2  | Other    | Diodes                                                | . 182               |

|   | A.3  | Three-   | -terminal Devices                                     | . 185               |

|   | A.4  | Distri   | buted Element Structures                              | . 189               |

| В | Mas  | sk-set [ | Drawings                                              | 190                 |

| С | Fab | rication of Quartz Circuits                                                                     | 200 |

|---|-----|-------------------------------------------------------------------------------------------------|-----|

|   | C.1 | Circuit Fabrication for the 55/110 GHz Frequency Doubler                                        | 200 |

|   | C.2 | Circuit Fabrication for the $110/220~\mathrm{GHz}$ Frequency Doubler $% 100/220~\mathrm{GHz}$ . | 204 |

|   | C.3 | Circuit Fabrication for the $80/240~{\rm GHz}$ Frequency Tripler                                | 206 |

| D | Med | chanical Drawings                                                                               | 211 |

| E | Ass | embly Procedures                                                                                | 260 |

|   | E.1 | Assembly of the 55/110 GHz Frequency Doubler                                                    | 260 |

|   | E.2 | Assembly of the 110/220 GHz Frequency Doubler $\hdots$                                          | 264 |

|   | E.3 | Assembly of the $80/240$ GHz Frequency Tripler $\ldots$                                         | 265 |

|   | E.4 | Assembly of the Modified $80/240$ GHz Frequency Tripler                                         | 268 |

# List of Figures

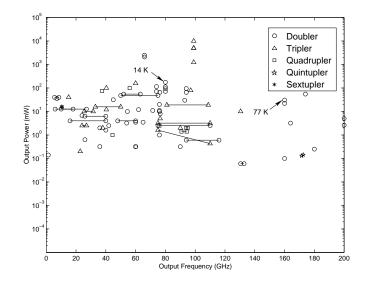

| 1.1 | State-of-the-art frequency multiplier performance survey (1991– |    |

|-----|-----------------------------------------------------------------|----|

|     | 2001): Output power versus frequency up to 200 GHz. See         |    |

|     | Appendix-A                                                      | 16 |

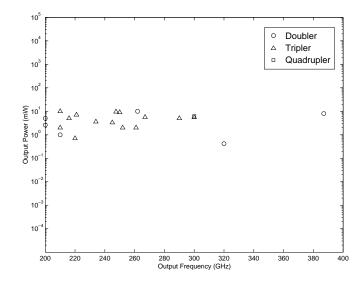

| 1.2 | State-of-the-art frequency multiplier performance survey (1991– |    |

|     | 2001): Output power versus frequency from 200 GHz to 400        |    |

|     | GHz. See Appendix-A                                             | 16 |

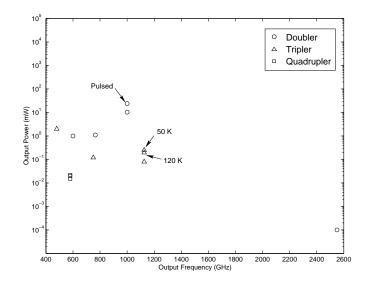

| 1.3 | State-of-the-art frequency multiplier performance survey (1991– |    |

|     | 2001): Output power versus frequency from 400 GHz to 2600 $$    |    |

|     | GHz. See Appendix-A                                             | 17 |

| 2.1 | A single diode based frequency doubler                          | 23 |

| 2.2 | An alternate doubler circuit employing a balanced diode         |    |

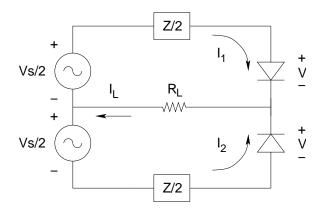

|     | configuration.                                                  | 24 |

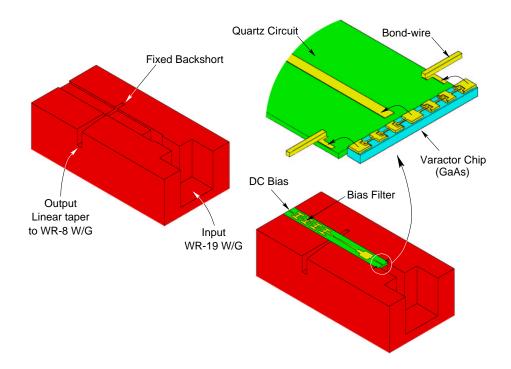

| 2.3 | The 55/100 GHz frequency doubler. Figure shows a cut-away       |    |

|     | view of the doubler mount revealing the location of the planar  |    |

|     | quartz circuit and the placement of the diode array on it       | 26 |

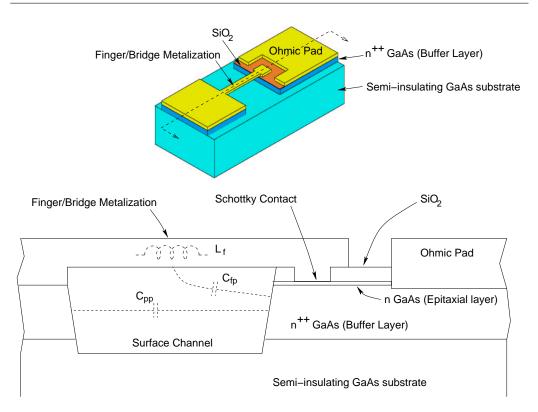

| 2.4 | Details of a planar Schottky varactor.                          | 29 |

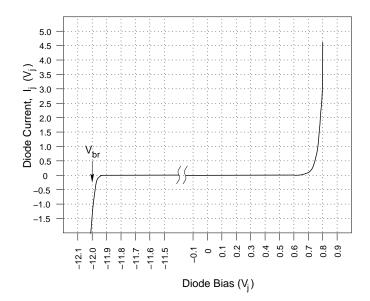

| 2.5 | Typical Current-Voltage relationship for a Schottky varactor    | 30 |

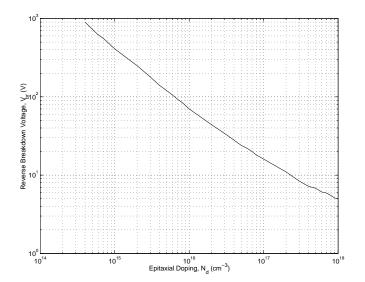

| 2.6  | Reverse breakdown voltages as a function of epitaxial layer         |    |

|------|---------------------------------------------------------------------|----|

|      | doping level                                                        | 32 |

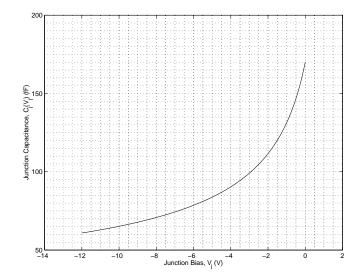

| 2.7  | Typical variation of the varactor junction capacitance with an      |    |

|      | applied (reverse) bias voltage.                                     | 33 |

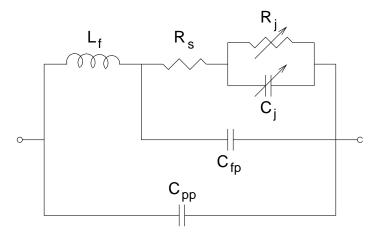

| 2.8  | Equivalent circuit model of a Schottky junction varactor diode.     | 36 |

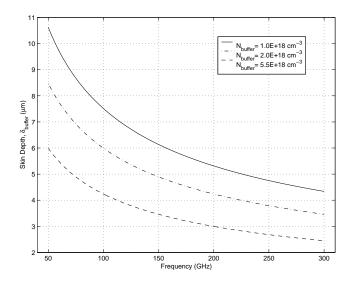

| 2.9  | Plot of skin depth in the buffer layer vs. frequency for three      |    |

|      | doping levels.                                                      | 37 |

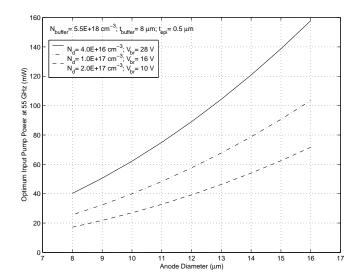

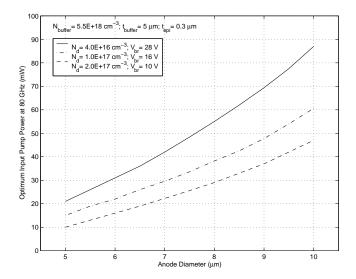

| 2.10 | Input power (per diode) to obtain maximum conversion ef-            |    |

|      | ficiency, for different anode sizes and epitaxial layer doping      |    |

|      | level                                                               | 38 |

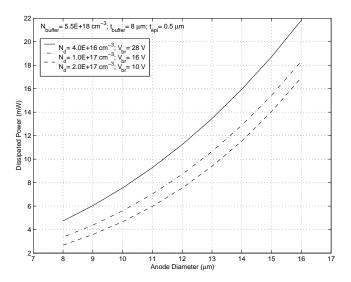

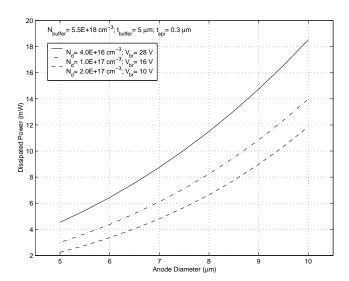

| 2.11 | Power dissipated (per diode) under conditions of optimum op-        |    |

|      | eration for different anode sizes and epitaxial layer doping level. | 38 |

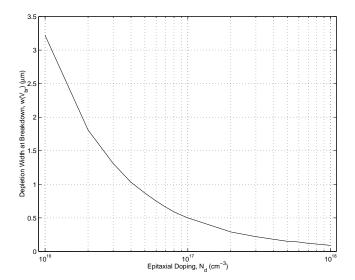

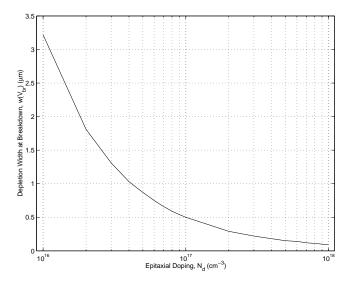

| 2.12 | Variation of the width of the depleted region in the epitaxial      |    |

|      | layer at before breakdown as a function of epitaxial doping level.  | 40 |

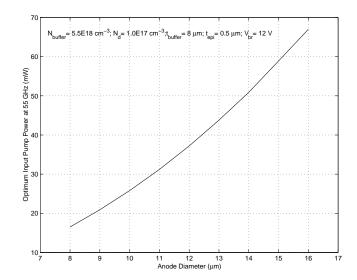

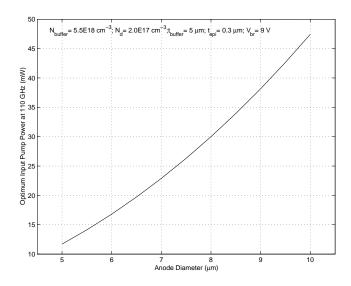

| 2.13 | Input power (per diode) to obtain maximum conversion effi-          |    |

|      | ciency for a range of anode sizes for the chosen material system.   | 41 |

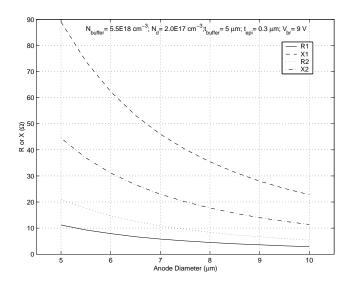

| 2.14 | Optimum embedding impedances as a function of anode size            | 42 |

| 2.15 | A Scanning Electron Micrograph of the UVA SB13T1 discrete           |    |

|      | planar Schottky varactor array used for the $55/110$ GHz fre-       |    |

|      | quency doubler design.                                              | 42 |

| 2.16 | The coaxial probe geometry employed to calculate the impedance      |    |

|      | at the location of the Schottky junctions                           | 47 |

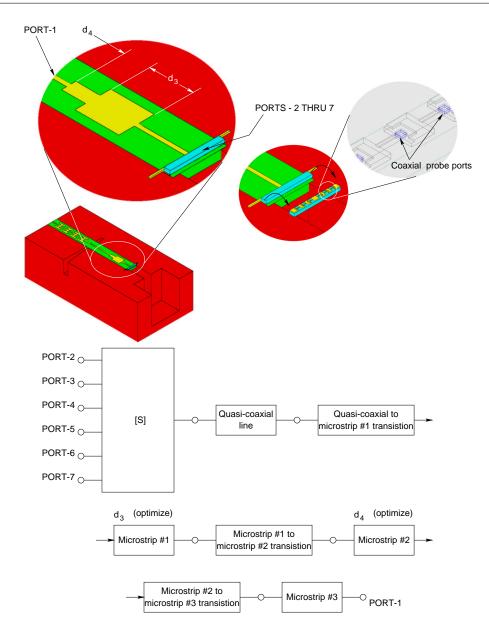

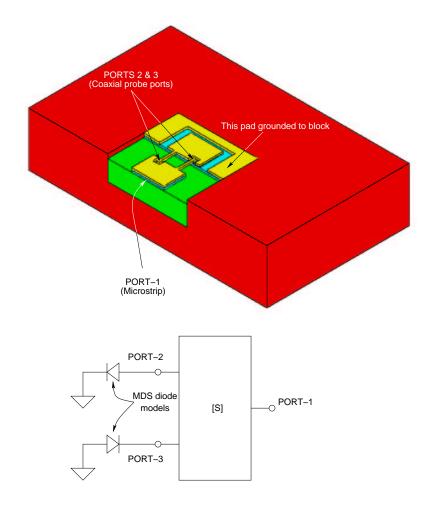

| 2.17 | Design of the input embedding circuit for the $55/110$ GHz fre-  |    |

|------|------------------------------------------------------------------|----|

|      | quency doubler. Only bottom half of the mount that seats the     |    |

|      | quartz circuit is shown, with and without the quartz circuit in  |    |

|      | place. The location of various ports as well as the dimensions   |    |

|      | that were optimized are illustrated. The equivalent circuit      |    |

|      | model schematic (based on the S-parameter files generated by     |    |

|      | HP-HFSS) used in MDS to optimize the lengths $d_1$ and $d_2$ in  |    |

|      | the input circuit is shown at the bottom                         | 50 |

| 2.18 | Design optimization of the impedance matching sections of        |    |

|      | the output embedding circuit for the $55/110$ GHz frequency      |    |

|      | doubler. Only bottom half of the mount that seats the quartz     |    |

|      | circuit is shown. The location of various ports as well as the   |    |

|      | dimensions that were optimized are illustrated. The equiva-      |    |

|      | lent circuit model schematic (based on the S-parameter files     |    |

|      | generated by HP-HFSS) used in MDS to optimize the lengths        |    |

|      | $d_3$ and $d_4$ in the output circuit is shown at the bottom     | 52 |

| 2.19 | Design of the bias filter. Only bottom half of the mount that    |    |

|      | seats the quartz circuit is shown. All the dimensions that were  |    |

|      | optimized are marked.                                            | 53 |

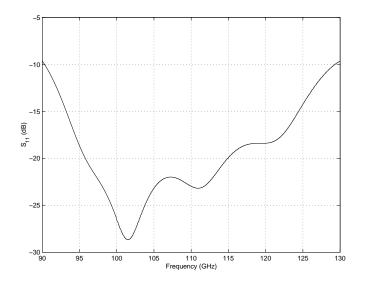

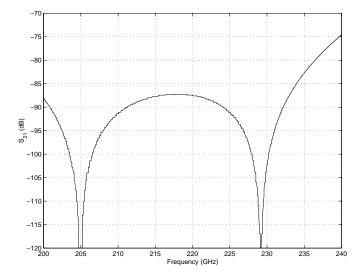

| 2.20 | Plot of $S_{21}$ for the DC bias filter (simulated)              | 54 |

|      | Plot of $S_{11}$ for the WR-8 one-fifth to full height waveguide | -  |

|      | linear taper (simulated).                                        | 55 |

|      | <b>1</b> · (· · · · · · · · · · · · · · · · · ·                  |    |

| 2.22 | ? Design of the output cross-guide coupler for the 55/110 GHz $-$         |    |

|------|---------------------------------------------------------------------------|----|

|      | frequency doubler. Only bottom half of the mount that seats               |    |

|      | the quartz circuit is shown. The dimensions that were opti-               |    |

|      | mized to achieve a good coupling efficiency are marked                    | 56 |

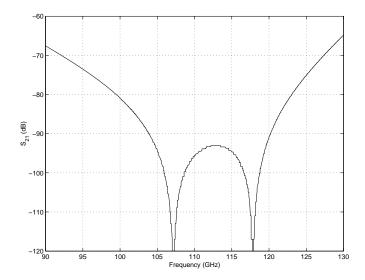

| 2.23 | Plot of $S_{11}$ for the complete output coupling arrangement,            |    |

|      | including the microstrip to one-fifth height waveguide probe,             |    |

|      | DC-bias filter and the one-fifth height to full height taper (sim-        |    |

|      | ulated).                                                                  | 57 |

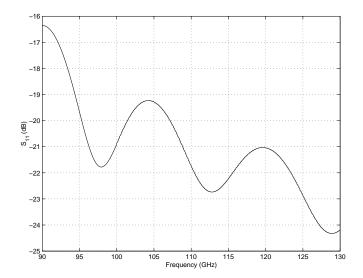

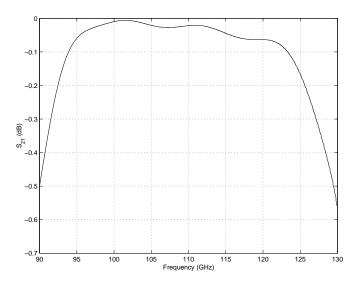

| 2.24 | Plot of $S_{21}$ for the complete output coupling arrangement,            |    |

|      | including the microstrip to one-fifth height waveguide probe,             |    |

|      | DC-bias filter and the one-fifth height to full height taper (sim-        |    |

|      | ulated).                                                                  | 57 |

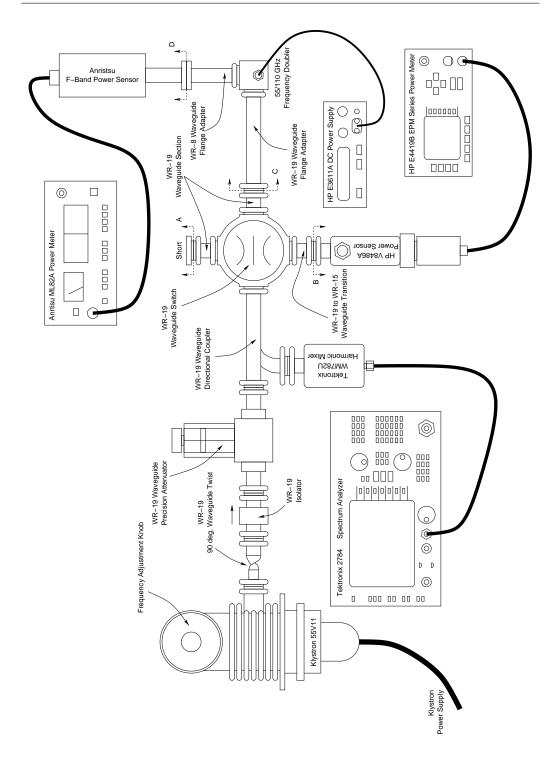

| 2.25 | Experimental setup for evaluation of the $55/110$ GHz fre-                |    |

|      | quency doubler.                                                           | 60 |

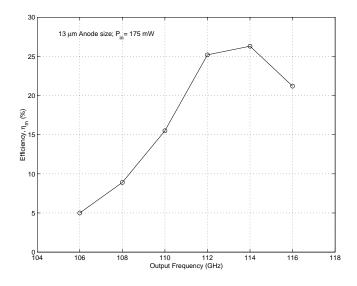

| 2.26 | Measured conversion efficiency of the $55/110$ GHz frequency              |    |

|      | doubler using a diode array with 13 $\mu m$ diameter anodes               | 62 |

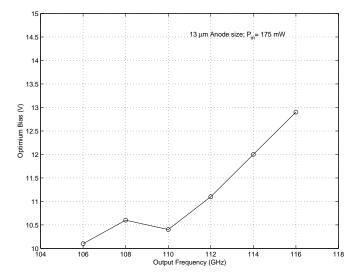

| 2.27 | Plot of the measured optimum bias voltage versus output fre-              |    |

|      | quency                                                                    | 63 |

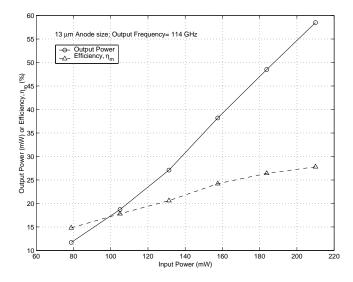

| 2.28 | <sup>8</sup> Measured output power and efficiency versus input pump power |    |

|      | for an output frequency of 114 GHz.                                       | 64 |

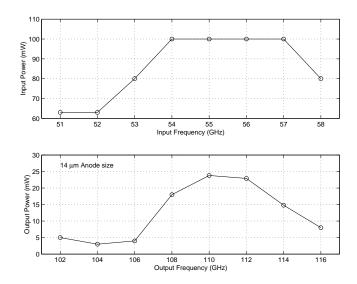

| 2.29 | Plot of the measured output power versus frequency for the                |    |

|      | 55/110 GHz frequency doubler using a diode array with 14 $\mu m$          |    |

|      | diameter anodes.                                                          | 65 |

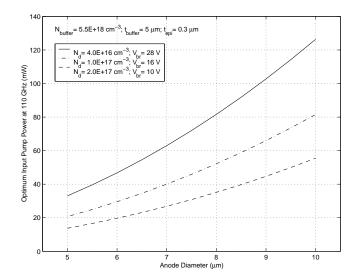

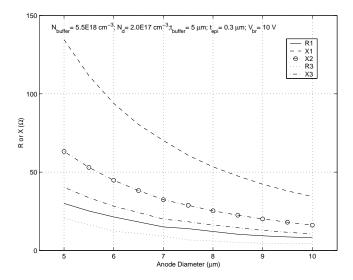

| 2.30 | Input power (per diode) to obtain maximum conversion ef-            |    |

|------|---------------------------------------------------------------------|----|

|      | ficiency, for different anode sizes and epitaxial layer doping      |    |

|      | level                                                               | 66 |

| 2.31 | Power dissipated (per diode) under conditions of optimum op-        |    |

|      | eration for different anode sizes and epitaxial layer doping level. | 67 |

| 2.32 | Input power (per diode) to obtain maximum conversion effi-          |    |

|      | ciency for a range of anode sizes for the chosen material system.   | 67 |

| 2.33 | Optimum embedding impedances as a function of anode size            | 68 |

| 2.34 | A Photograph of the UVA SB7T7 discrete planar Schottky              |    |

|      | varactor array used for the $110/220$ GHz frequency doubler         |    |

|      | design                                                              | 68 |

| 2.35 | Plot of $S_{21}$ for the DC bias filter (simulated)                 | 70 |

| 2.36 | Plot of $S_{11}$ for the WR-4 one-fifth to full height waveguide    |    |

|      | linear taper (simulated).                                           | 70 |

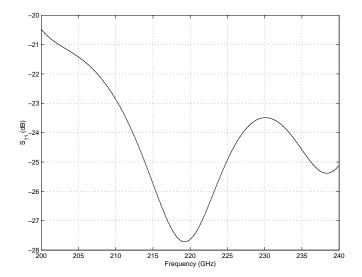

| 2.37 | Plot of $S_{11}$ for the complete output coupling arrangement,      |    |

|      | including the microstrip to one-fifth height waveguide probe,       |    |

|      | DC-bias filter and the one-fifth height to full height taper (sim-  |    |

|      | ulated).                                                            | 71 |

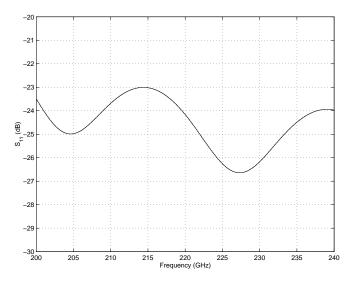

| 2.38 | Plot of $S_{21}$ for the complete output coupling arrangement,      |    |

|      | including the microstrip to one-fifth height waveguide probe,       |    |

|      | DC-bias filter and the one-fifth height to full height taper (sim-  |    |

|      | ulated).                                                            | 71 |

| 2.39 | Experimental setup for evaluation of the $110/220$ GHz fre-         |    |

|      | quency doubler.                                                     | 74 |

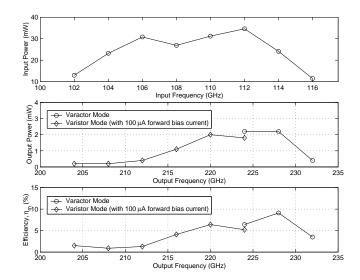

| 2.40 | Measured performance of the $110/220$ GHz frequency doubler,     |    |

|------|------------------------------------------------------------------|----|

|      | built using a diode array having anodes with 8 $\mu m$ diameter  | 76 |

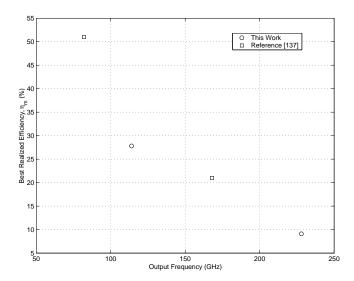

| 2.41 | Plot of the best reported and measured efficiencies of various   |    |

|      | frequency doublers built based on the hybrid approach            | 79 |

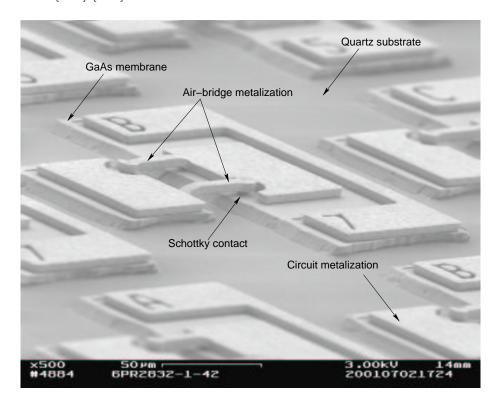

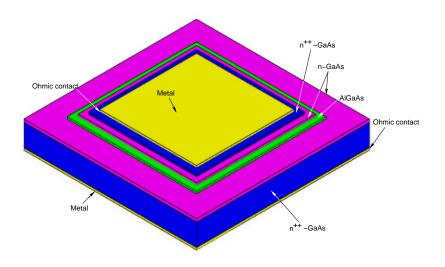

| 3.1  | A Scanning Electron Micrograph of an undiced wafer fabri-        |    |

|      | cated based on the composite GaAs-membrane-on-quartz ap-         |    |

|      | proach. Photograph courtesy Gerhard S. Schoenthal, Univer-       |    |

|      | sity of Virginia, Semiconductor Development Laboratory           | 84 |

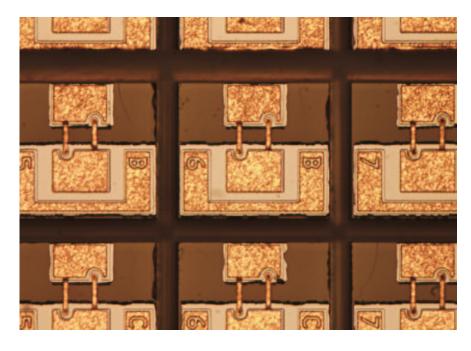

| 3.2  | Photograph of the diced wafer prior to backside lapping to       |    |

|      | achieve chip separation. Photograph courtesy Gerhard S. Schoen-  |    |

|      | thal, University of Virginia, Semiconductor Development Lab-     |    |

|      | oratory.                                                         | 85 |

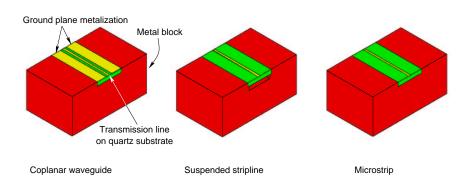

| 3.3  | Planar transmission line structures.                             | 87 |

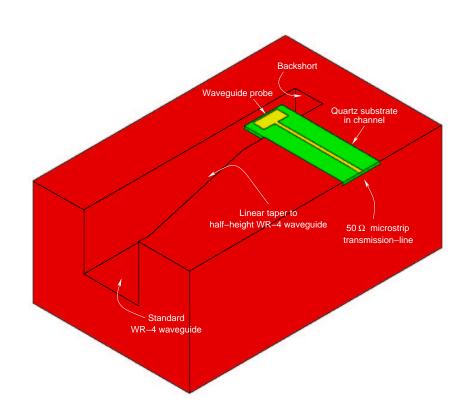

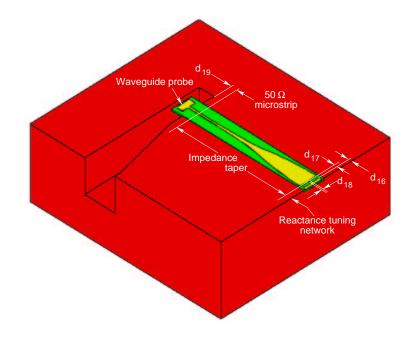

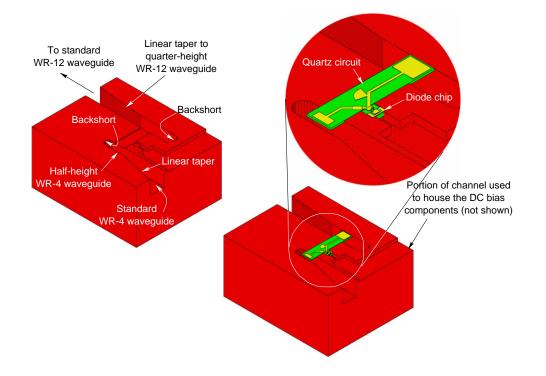

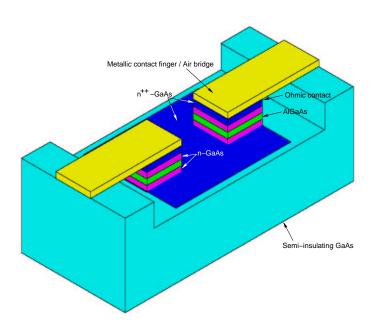

| 3.4  | The microstrip to WR-4 waveguide transition. Figure shows        |    |

|      | a cut-away view of the arrangement. Only the bottom half of      |    |

|      | the block is illustrated, revealing the placement of the quartz  |    |

|      | circuit in the metal housing.                                    | 88 |

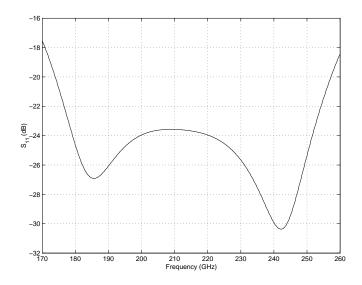

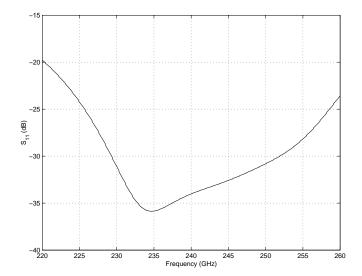

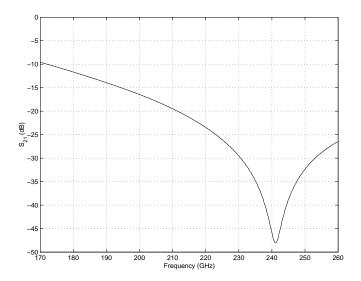

| 3.5  | Plot of $S_{11}$ for the microstrip to WR-4 waveguide transition |    |

|      | of Figure-3.4.                                                   | 89 |

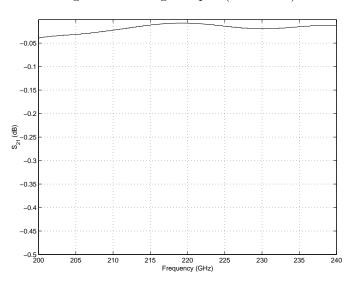

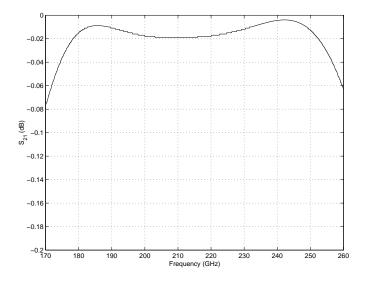

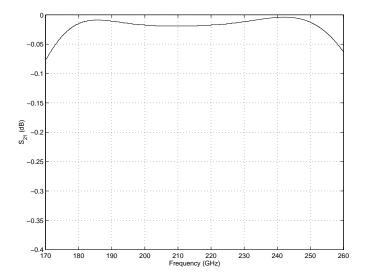

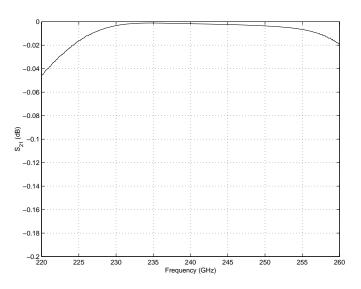

| 3.6  | Plot of $S_{21}$ for the microstrip to WR-4 waveguide transition |    |

|      | of Figure-3.4.                                                   | 89 |

| 3.7  | Photograph of 2 mil thick quartz circuit showing the test ca-    |    |

|      | pacitor at one end of the microstrip transmission line. The      |    |

|      | waveguide probe is visible as a "flag" structure on the other    |    |

|      | end of the microstrip                                            | 91 |

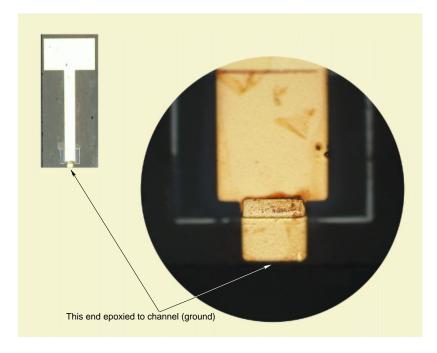

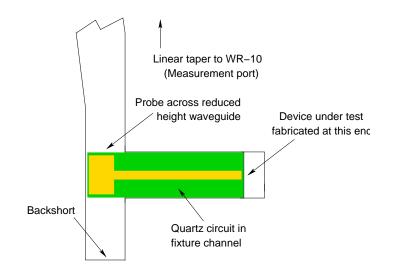

| 3.8  | Cut away view of the test fixture, showing the placement of             |

|------|-------------------------------------------------------------------------|

|      | quartz circuit with the device under test inside                        |

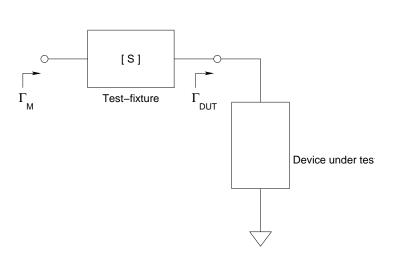

| 3.9  | Block diagram of the experimental setup                                 |

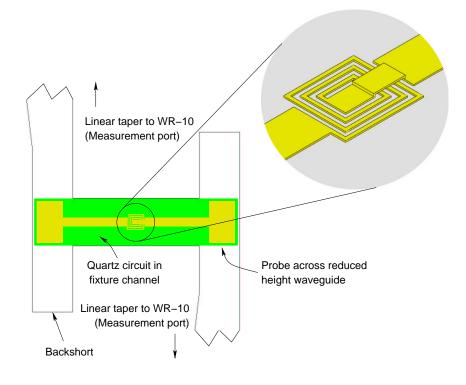

| 3.10 | The circuit used for the evaluation of the planar integrated            |

|      | inductor element $[154]$                                                |

| 3.11 | Plot of the simulated values of $S_{21}$ for the spiral inductor struc- |

|      | ture of Figure-3.10                                                     |

| 3.12 | Plot of the measured values of $S_{21}$ for the spiral inductor struc-  |

|      | ture of Figure-3.10                                                     |

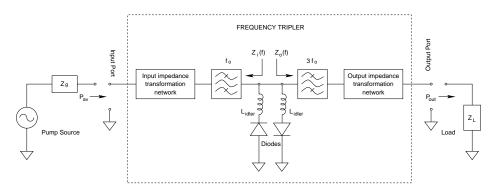

| 4.1  | A single diode based frequency tripler                                  |

|      |                                                                         |

| 4.2  | An alternate tripler circuit employing anti-parallel diode              |

|      | arrangement                                                             |

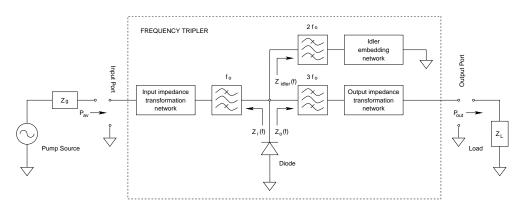

| 4.3  | A practical frequency tripler circuit configuration based on            |

|      | anti-parallel arrangement of diodes                                     |

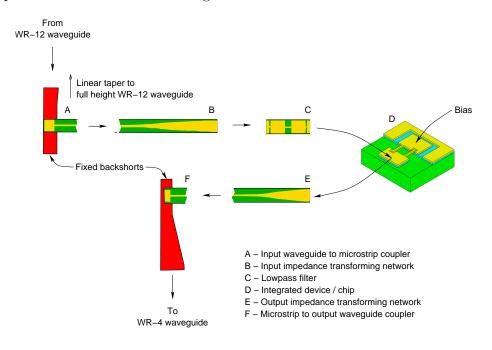

| 4.4  | Relative placement of various components used in the $80/240$           |

|      | GHz frequency tripler                                                   |

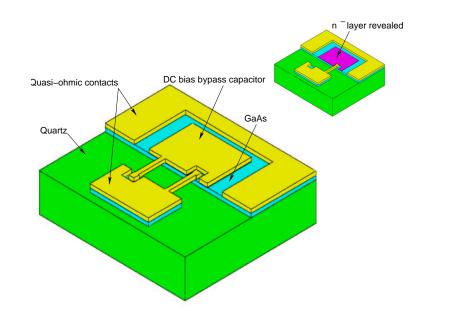

| 4.5  | Layout of the quartz based integrated device, consisting of two         |

|      | Schottky diodes in an anti-parallel configuration and a large           |

|      | capacitor to accommodate the DC bias arrangement. The                   |

|      | smaller inset is a view with the top metalization of capacitor          |

|      | removed to reveal the $n^-$ layer underneath                            |

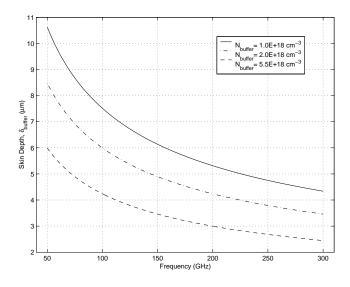

| 4.6  | Plot of skin depth in the buffer layer vs. frequency for three          |

|      | doping levels                                                           |

| 4.7  | Input power (per diode) to obtain maximum conversion ef-              |

|------|-----------------------------------------------------------------------|

|      | ficiency, for different anode sizes and epitaxial layer doping        |

|      | level                                                                 |

| 4.8  | Variation of the width of the depleted region in the epitaxial        |

|      | layer at before breakdown as a function of epitaxial doping level.115 |

| 4.9  | Optimum embedding impedances as a function of anode size 116          |

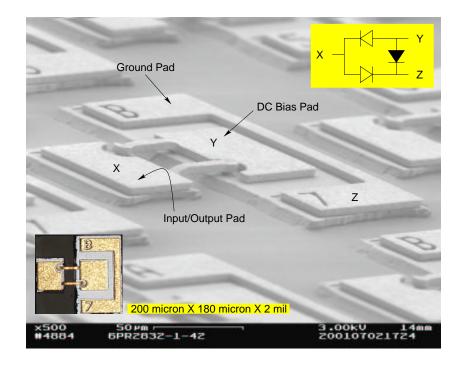

| 4.10 | A Scanning Electron Micrograph of a completed wafer of the            |

|      | quartz based integrated devices, prior to the dicing operation.       |

|      | The location of some significant terminals is identified. The         |

|      | "open" diode symbols represent Schottky contacts, while the           |

|      | black filled diode symbol represents the location of the DC bias      |

|      | bypass capacitor. A photograph of a diced chip together with          |

|      | its dimensions is included at the bottom. Photograph courtesy         |

|      | Gerhard S. Schoenthal, University of Virginia, Semiconductor          |

|      | Development Laboratory. See also Figure-3.1                           |

| 4.11 | Cut away view of the structure analyzed in HP-HFSS to com-            |

|      | pute the S-parameters of the frequency tripler chip. Only bot-        |

|      | tom half of the mount that seats the diode chip is shown. Also        |

|      | shown at the bottom is the equivalent circuit model schematic         |

|      |                                                                       |

shown at the bottom is the equivalent circuit model schematic (based on the calculated S-parameters) used in MDS to perform harmonic balance simulations to calculate the optimum input and output embedding impedances. For simplicity, the

DC bias arrangement has been omitted and is not shown. . . . 118

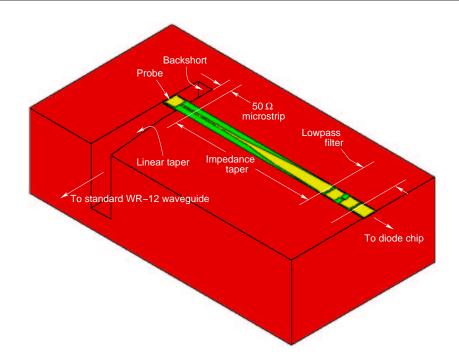

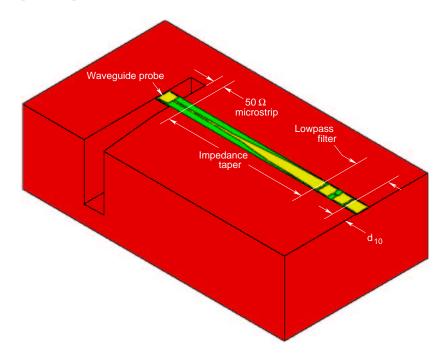

| 4.12 | The input embedding circuit consisting of a waveguide to mi-             |

|------|--------------------------------------------------------------------------|

|      | crostrip transition, a microstrip impedance taper and a low-             |

|      | pass filter. Only the bottom part of the mount that seats the            |

|      | quartz circuit is shown                                                  |

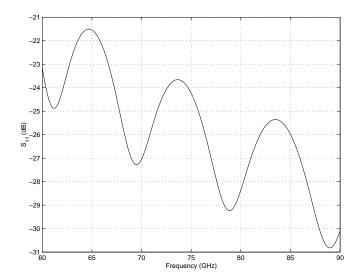

| 4.13 | Plot of $S_{11}$ for the WR-12 one-fourth to full height waveguide       |

|      | linear taper (simulated)                                                 |

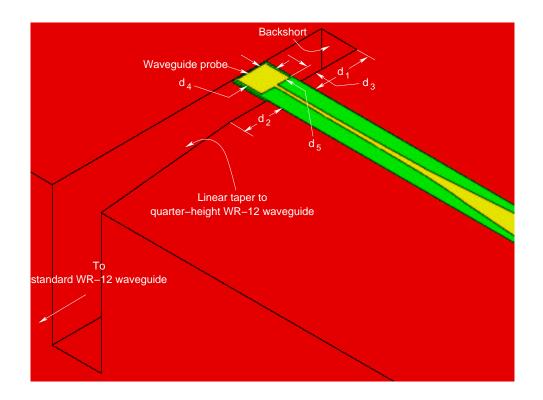

| 4.14 | Design of the input coupler for the $80/240$ GHz frequency               |

|      | tripler. Only bottom part of the mount that seats the quartz             |

|      | circuit is shown. The dimensions that were optimized to achieve          |

|      | a good coupling efficiency are marked                                    |

| 4.15 | Plot of $S_{11}$ for the input WR-12 waveguide to 50 $\Omega$ microstrip |

|      | transition (simulated)                                                   |

| 4.16 | Plot of $S_{21}$ for the input WR-12 waveguide to 50 $\Omega$ microstrip |

|      | transition (simulated)                                                   |

| 4.17 | Design of the input lowpass filter. Only bottom part of the              |

|      | mount that seats the quartz circuit is shown. All the dimen-             |

|      | sions that were optimized are marked                                     |

| 4.18 | Plot of $S_{21}$ for the input lowpass filter (simulated)                |

| 4.19 | The complete input embedding circuit consisting of a waveg-              |

|      | uide to microstrip transition, a microstrip impedance taper              |

|      | and a lowpass filter. Only the bottom part of the mount that             |

|      | seats the quartz circuit is shown. The length of the section             |

|      | marked $d_{10}$ was optimized such that the impedance presented          |

|      | to the diode chip was close to an open circuit at the output             |

|      | frequency of 240 GHz                                                     |

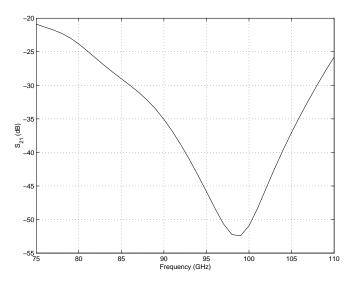

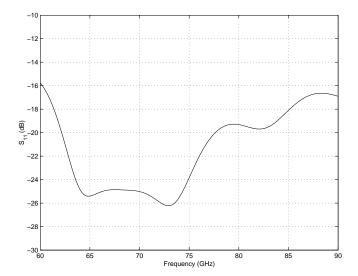

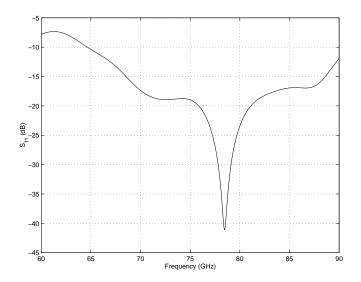

| 4.20 | Plot of $S_{11}$ for the complete 80/240 GHz frequency tripler           |

|------|--------------------------------------------------------------------------|

|      | input circuit (simulated)                                                |

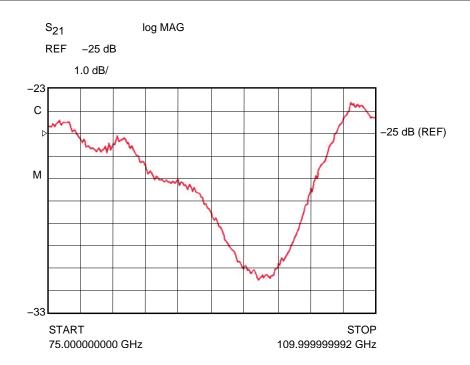

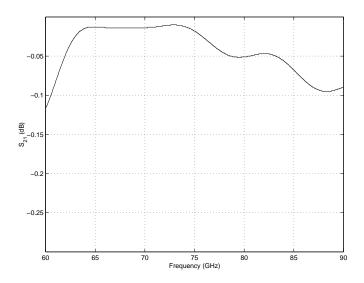

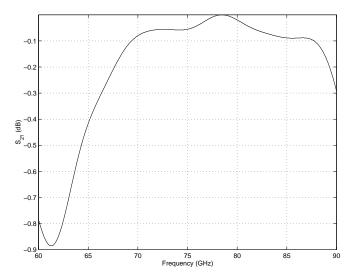

| 4.21 | Plot of $S_{21}$ for the complete 80/240 GHz frequency tripler           |

|      | input circuit (simulated)                                                |

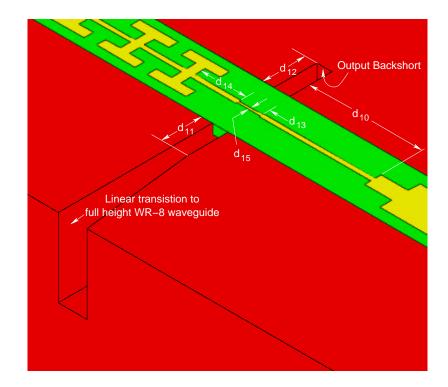

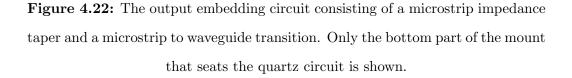

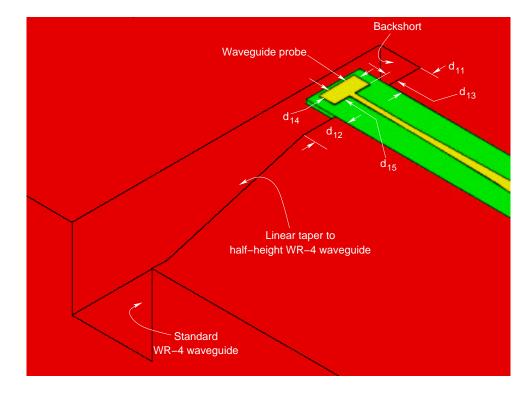

| 4.22 | The output embedding circuit consisting of a microstrip impedance        |

|      | taper and a microstrip to waveguide transition. Only the bot-            |

|      | tom part of the mount that seats the quartz circuit is shown $128$       |

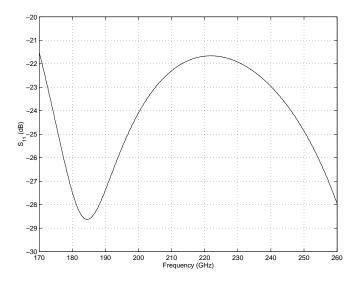

| 4.23 | Plot of $S_{11}$ for the WR-4 half height to full height waveguide       |

|      | linear taper (simulated)                                                 |

| 4.24 | Design of the output coupler for the $80/240$ GHz frequency              |

|      | tripler. Only bottom part of the mount that seats the quartz             |

|      | circuit is shown. The dimensions that were optimized to achieve          |

|      | a good coupling efficiency are marked                                    |

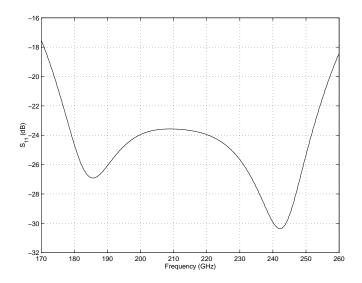

| 4.25 | Plot of $S_{11}$ for the output 50 $\Omega$ microstrip to WR-4 waveguide |

|      | transition (simulated)                                                   |

| 4.26 | Plot of $S_{21}$ for the output 50 $\Omega$ microstrip to WR-4 waveguide |

|      | transition (simulated)                                                   |

| 4.27 | The output embedding circuit consisting of a reactance tuning            |

|      | structure followed by a microstrip impedance taper and a mi-             |

|      | crostrip to waveguide transition. Only the bottom part of the            |

|      | mount that seats the quartz circuit is shown. The length of              |

|      | the section marked $d_{16}$ was optimized such that the impedance        |

|      | presented to the diode chip was close to an open circuit at the          |

|      | input frequency of 80 GHz                                                |

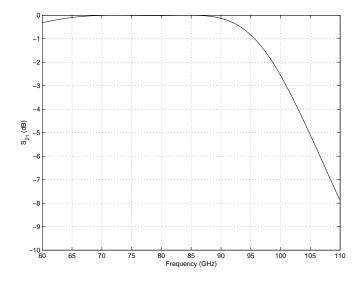

| 4.28 | Plot of $S_{11}$ for the complete 80/240 GHz frequency tripler |

|------|----------------------------------------------------------------|

|      | output circuit (simulated)                                     |

| 4.29 | Plot of $S_{21}$ for the complete 80/240 GHz frequency tripler |

|      | output circuit (simulated)                                     |

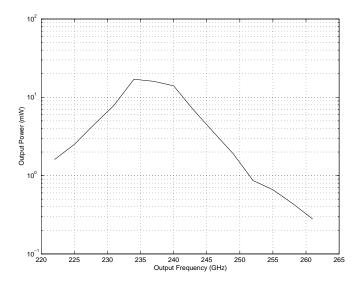

| 4.30 | Calculated output power of the $80/240$ GHz frequency tripler  |

|      | as a function of output frequency                              |

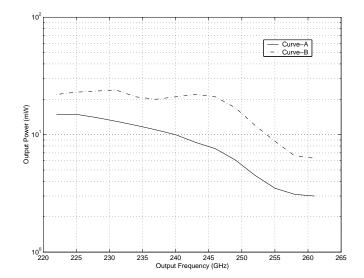

| 4.31 | Calculated output power of the $80/240$ GHz frequency tripler  |

|      | with the mutual loading effects between the input and out-     |

|      | put circuits ignored (curve-A). Curve-B shows the calculated   |

|      | output power with nearly ideal embedding impedances 135        |

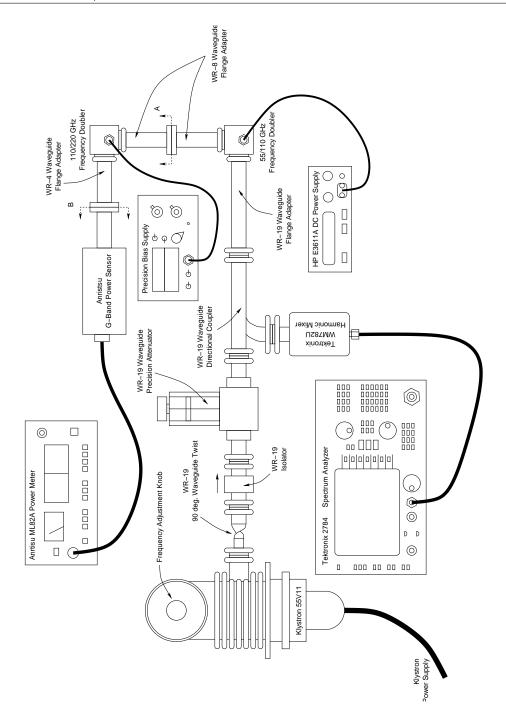

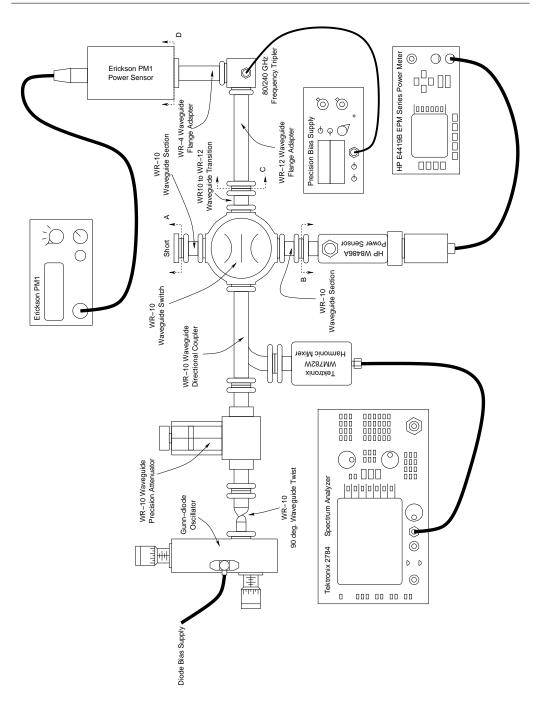

| 4.32 | Experimental setup for evaluation of the $80/240$ GHz fre-     |

|      | quency tripler                                                 |

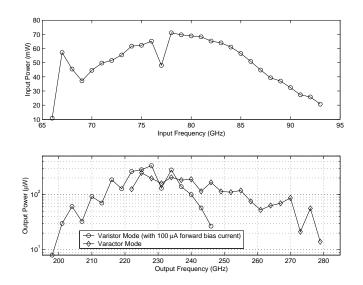

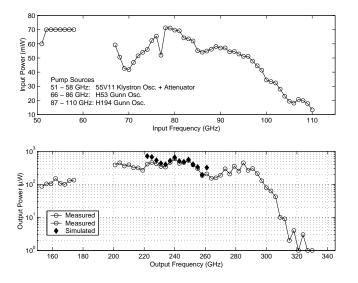

| 4.33 | Measured performance of the $80/240$ GHz frequency tripler,    |

|      | built using a diode chip having 6 $\mu m$ diameter anodes 140  |

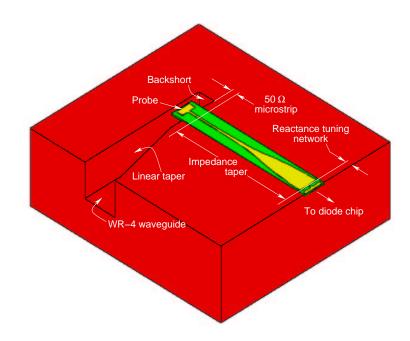

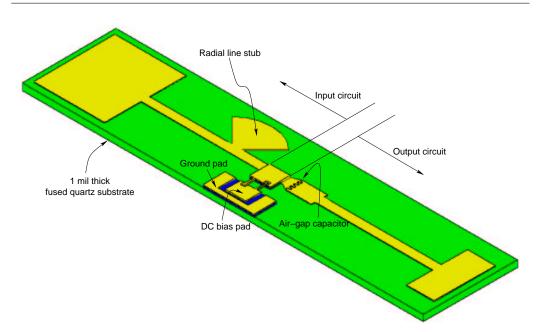

| 4.34 | The modified $80/240$ GHz frequency tripler. Figure shows a    |

|      | cut-away view of the split block mount revealing the location  |

|      | of the planar quartz circuit and the placement of the diode    |

|      | chip alongside it. The DC bias components and bond wires       |

|      | are omitted                                                    |

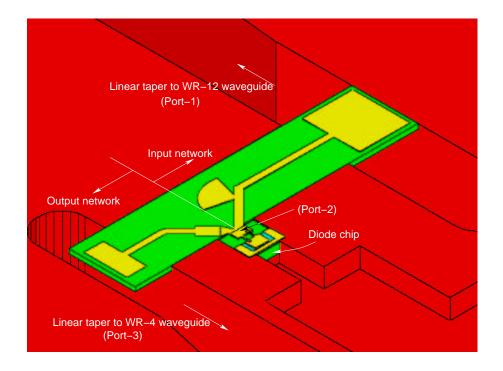

| 4.35 | Layout of the input and output embedding circuits, integrated  |

|      | onto a single quartz substrate. Also illustrated is the place- |

|      | ment of the quartz circuit relative to important features on   |

|      | the metal block as well as the diode chip. Only bottom half    |

|      | of the mount that seats the circuits is shown                  |

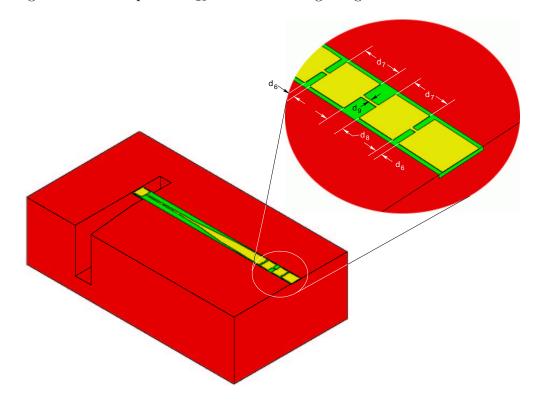

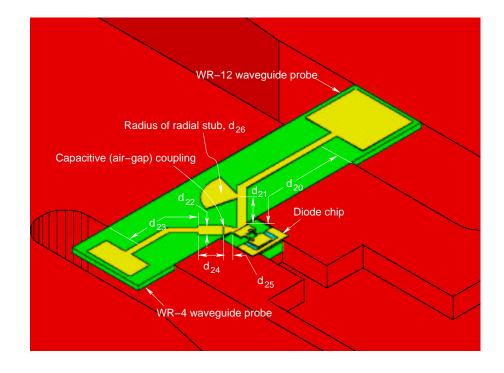

| 4.36 | Design of the input and output embedding circuits. All the          |     |

|------|---------------------------------------------------------------------|-----|

|      | dimensions that were optimized are marked. The design of            |     |

|      | the 50 $\Omega$ microstrip to waveguide transition for both the in- |     |

|      | put and output was carried forward from the previous block.         |     |

|      | Consequently, dimensions corresponding to those transitions         |     |

|      | did not need to be optimized. Only bottom half of the mount         |     |

|      | that seats the circuits is shown.                                   | 144 |

| 4.37 | Plot of $S_{21}$ for the modified 80/240 GHz frequency tripler      |     |

|      | quartz circuit showing the isolation provided by the radial stub    |     |

|      | in the input circuit to the third harmonic signals (simulated).     | 145 |

| 4.38 | Performance of the modified $80/240$ GHz frequency tripler          |     |

|      | built using a diode chip having 6 $\mu m$ diameter anodes, with     |     |

|      | the DC bias bypass capacitor shorted to the ground pad with         |     |

|      | silver epoxy                                                        | 146 |

| 4.39 | Layout of the $80/240$ GHz frequency tripler as a MMIC chip.        |     |

|      | The embedding circuits may be fabricated integrally as shown        |     |

|      | on the extended GaAs-membrane-on-quartz substrate after             |     |

|      | the removal of GaAs from appropriate regions                        | 148 |

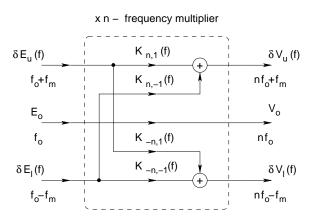

| 5.1  | Transmission of sideband noise through a frequency multiplier,      |     |

| 0.1  | considered as a linear frequency converter.                         | 159 |

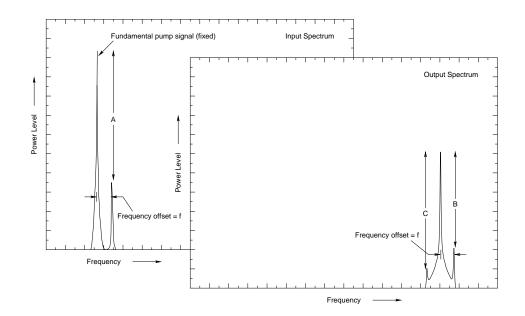

| 5.2  | Sketches illustrate the power spectrum of the test input signal     | 105 |

| 0.2  | used in two-tone harmonic balance simulations (left) and the        |     |

|      |                                                                     | 161 |

|      | typical resulting output power spectrum (right)                     | 101 |

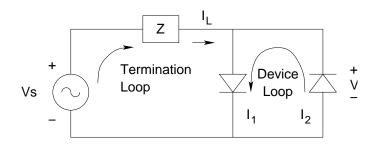

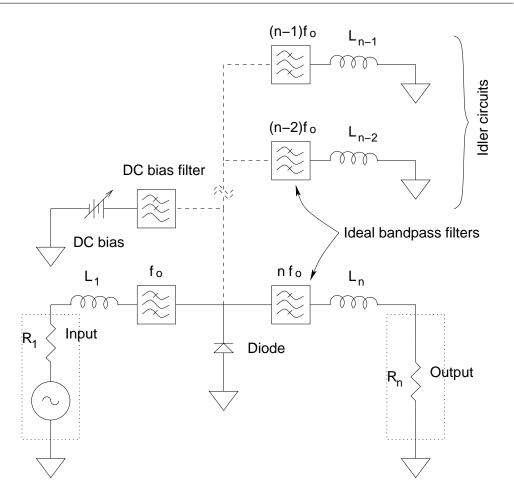

| 5.3 | Generalized configuration of the circuit used in two-tone har-      |

|-----|---------------------------------------------------------------------|

|     | monic balance simulations to evaluate the up-conversion of          |

|     | amplitude-noise sidebands in $\times n$ single-diode frequency mul- |

|     | tipliers. The idler and bias circuits were used, as appropriate,    |

|     | for setting up various frequency multipler simulations 163          |

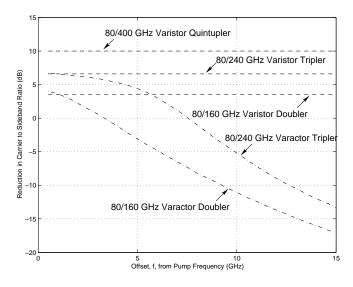

| 5.4 | Plot of the degradation in carrier-to-sideband ratio for various    |

|     | frequency multipliers                                               |

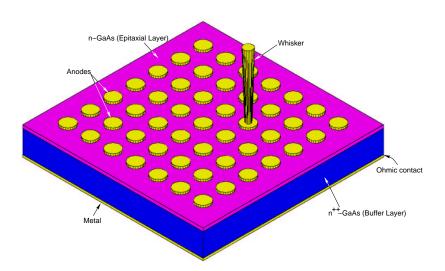

| A.1 | Whisker contacted abrupt junction Schottky diode 176                |

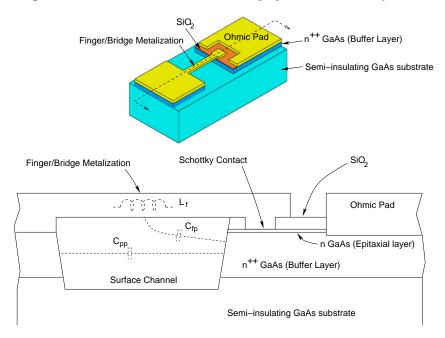

| A.2 | Planarized abrupt junction Schottky diode                           |

| A.3 | Discrete hetero-junction barrier varactor diode                     |

| A.4 | Planarized hetero-junction barrier varactor diode                   |

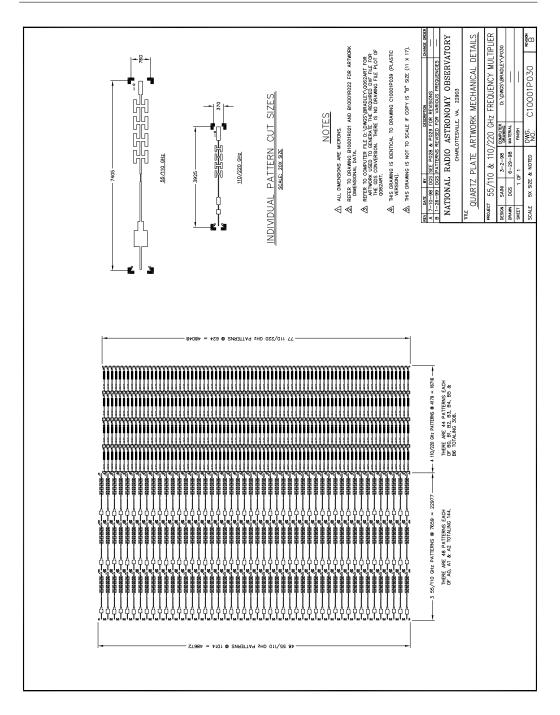

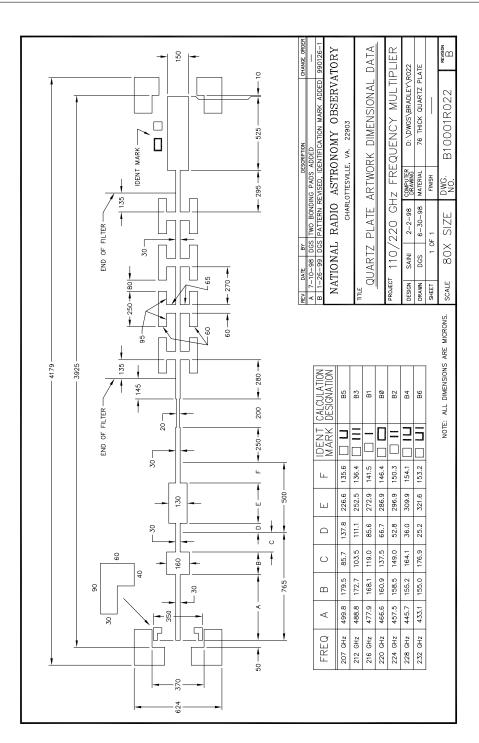

| B.1 | Details of the mask set used in the fabrication of quartz circuits  |

|     | for the 55/110 GHz and 110/220 GHz frequency doublers. $$ 191       |

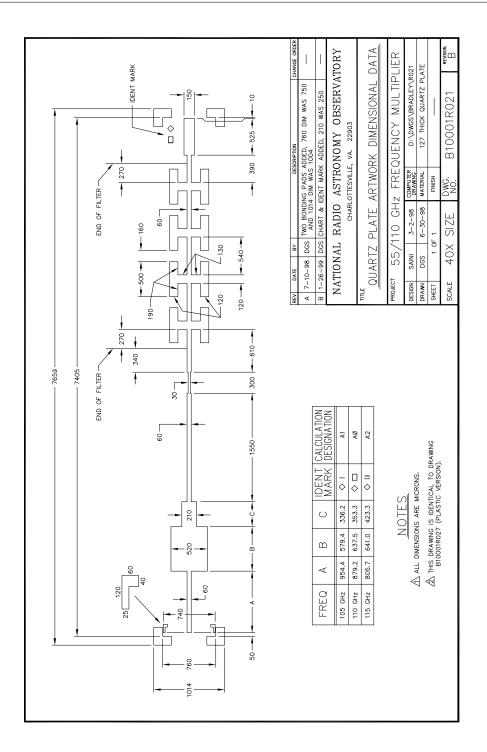

| B.2 | Dimensional details of the artwork representing the metaliza-       |

|     | tion pattern on an individual quartz circuit used in the $55/110$   |

|     | GHz frequency doubler                                               |

| B.3 | Dimensional details of the artwork representing the metal-          |

|     | ization pattern on an individual quartz circuit used in the         |

|     | 110/220 GHz frequency doubler                                       |

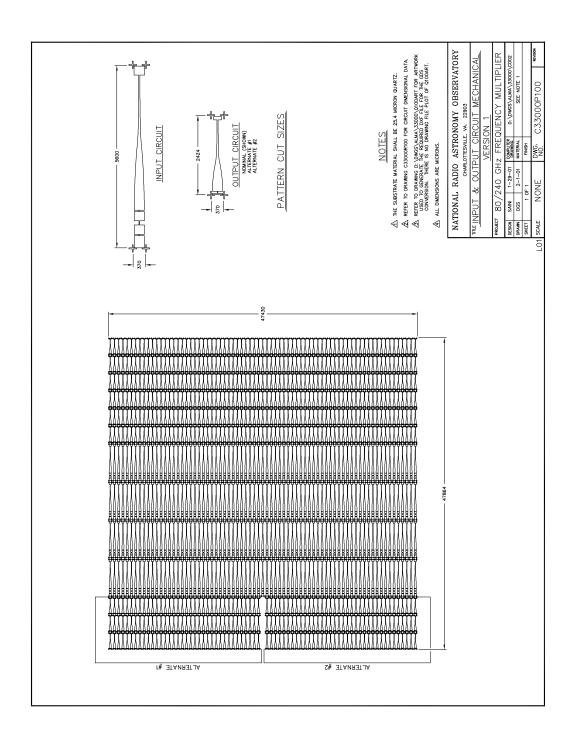

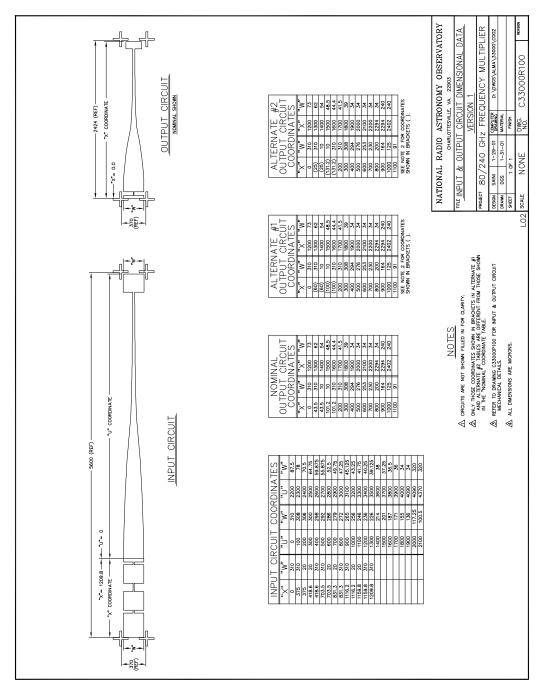

| B.4 | Details of the mask set used in the fabrication of input and        |

|     | output quartz circuits for the $80/240$ GHz frequency tripler       |

|     | (version 1)                                                         |

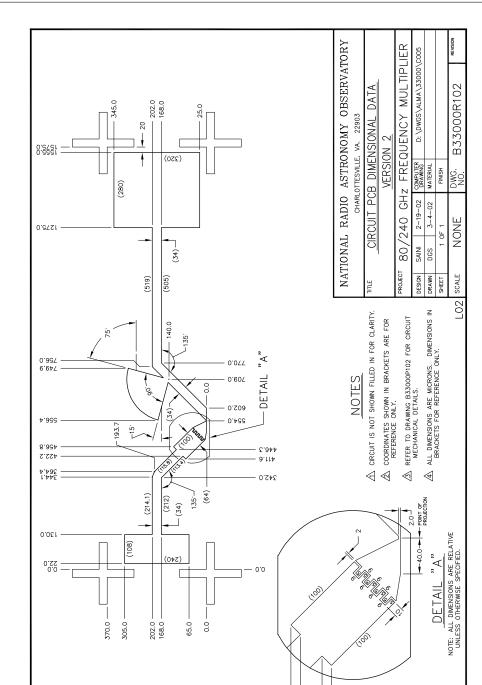

| B.5 | Dimensional details of the artwork representing the input and       |

|     | output metalization patterns for the quartz circuits used in        |

|     | the $80/240$ GHz frequency tripler (version 1)                      |

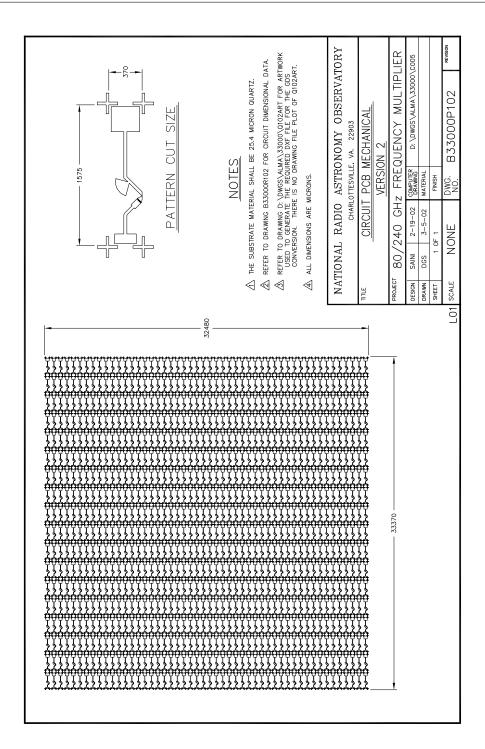

| B.6 | Details of the mask set used in the fabrication of quartz circuits    |

|-----|-----------------------------------------------------------------------|

|     | for the $80/240$ GHz frequency tripler (version 2)                    |

| B.7 | Dimensional details of the artwork representing the metaliza-         |

|     | tion pattern on an individual quartz circuit used in the $80/240$     |

|     | GHz frequency tripler (version 2)                                     |

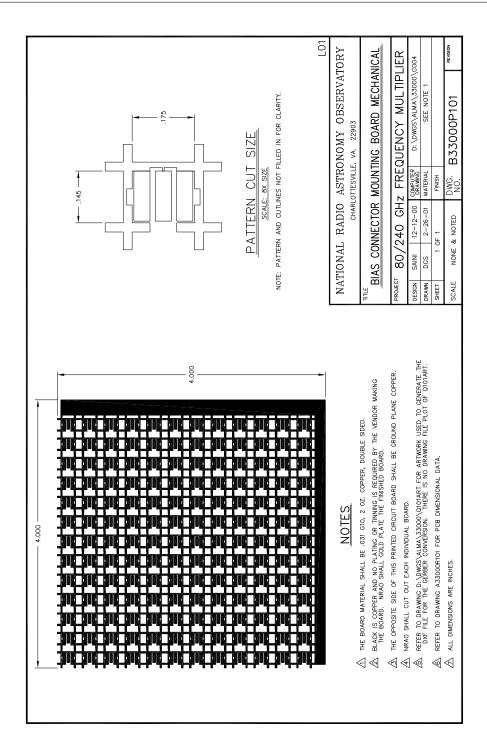

| B.8 | Details of the artwork film used in the fabrication of printed        |

|     | circuit board for the DC bias circuit in the $80/240$ GHz fre-        |

|     | quency tripler                                                        |

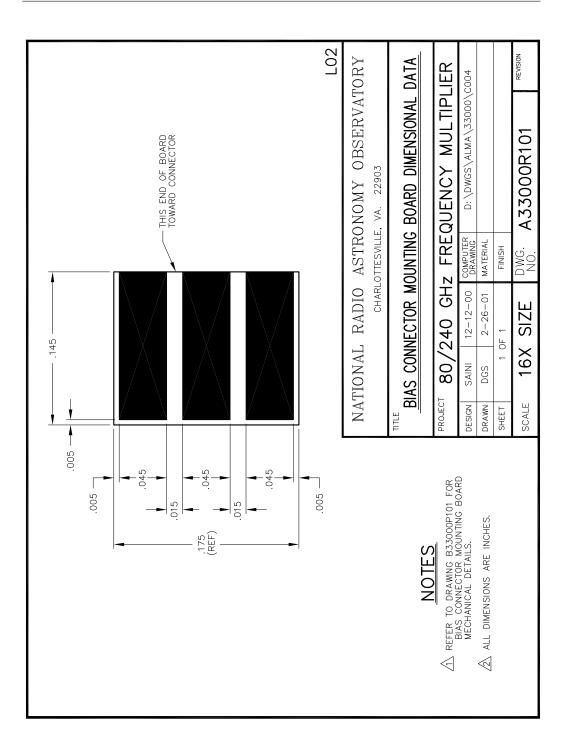

| B.9 | Dimensional details of the artwork representing the metaliza-         |

|     | tion pattern on an individual DC bias board used in the $80/240$      |

|     | GHz frequency tripler                                                 |

| D 1 |                                                                       |

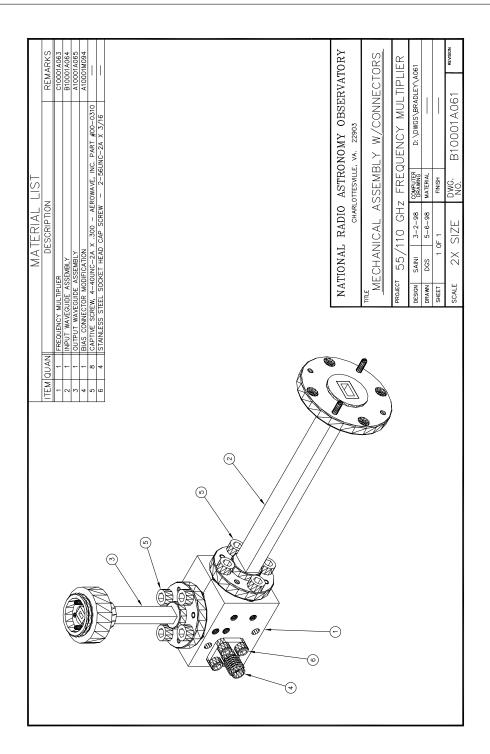

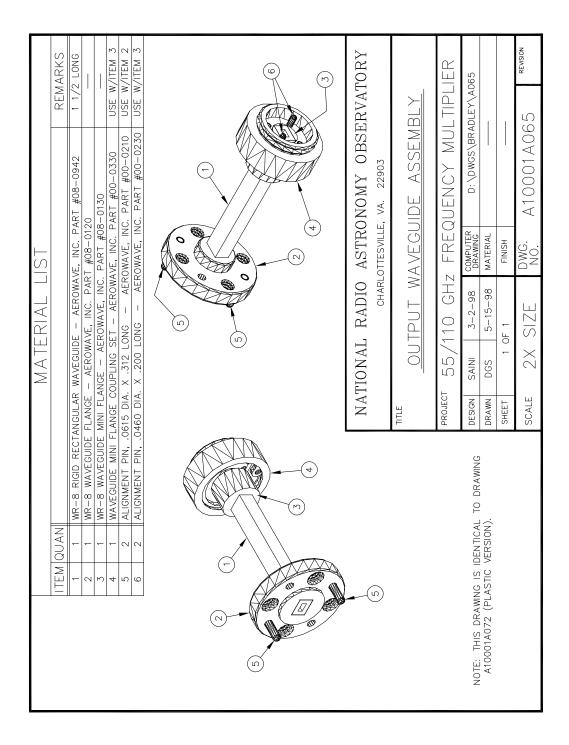

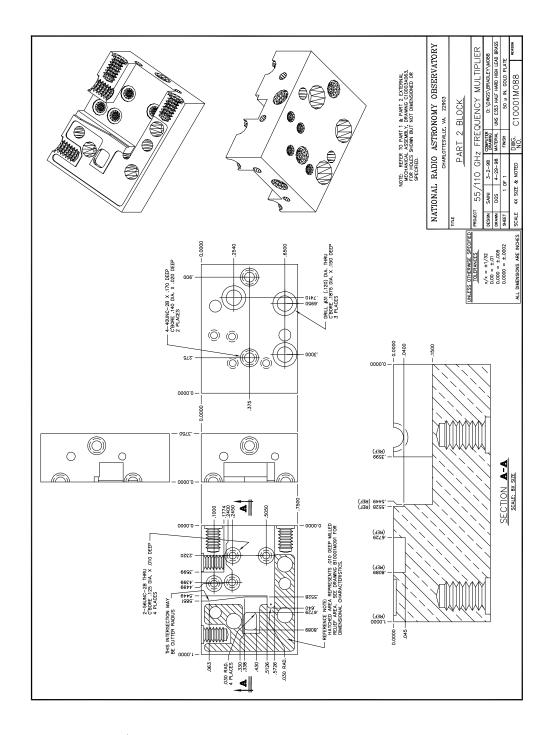

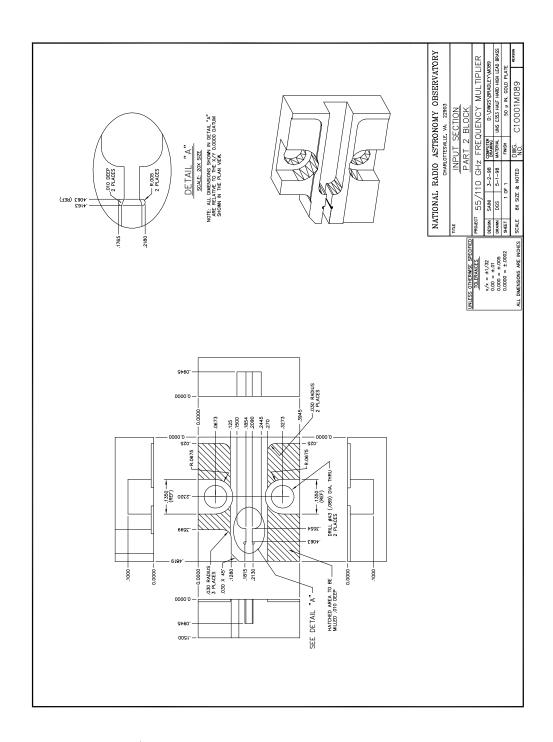

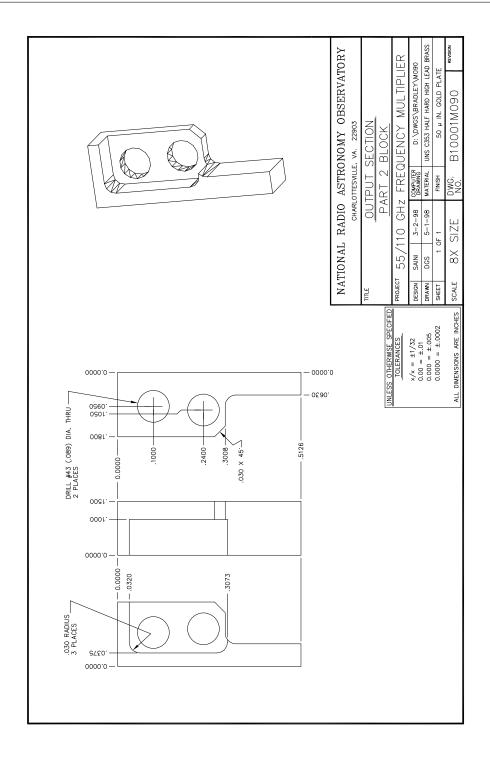

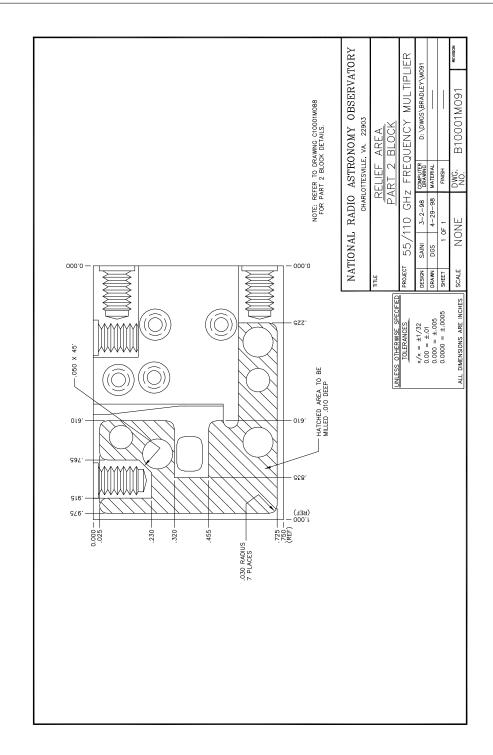

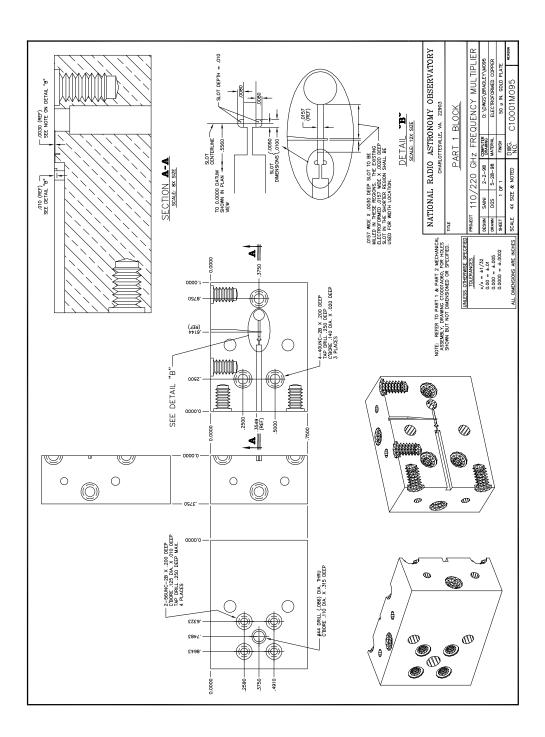

| D.1 | 55/110 GHz frequency doubler: Mechanical assembly of the              |

|     | split block showing the DC bias connector and the waveguide           |

|     | flange adapters                                                       |

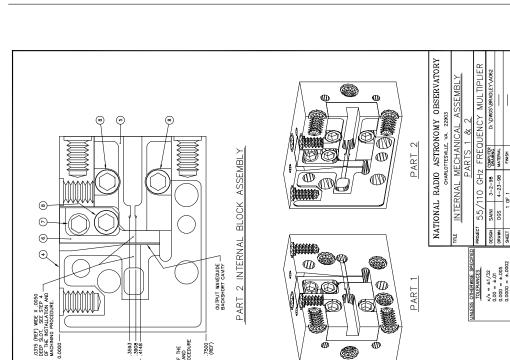

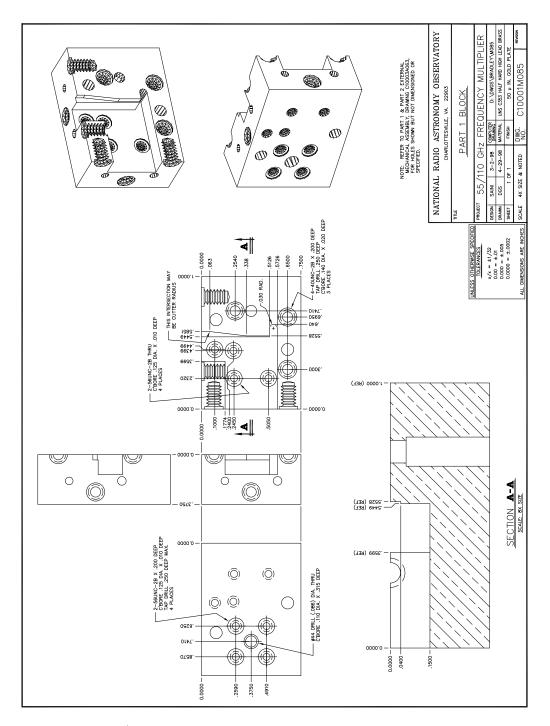

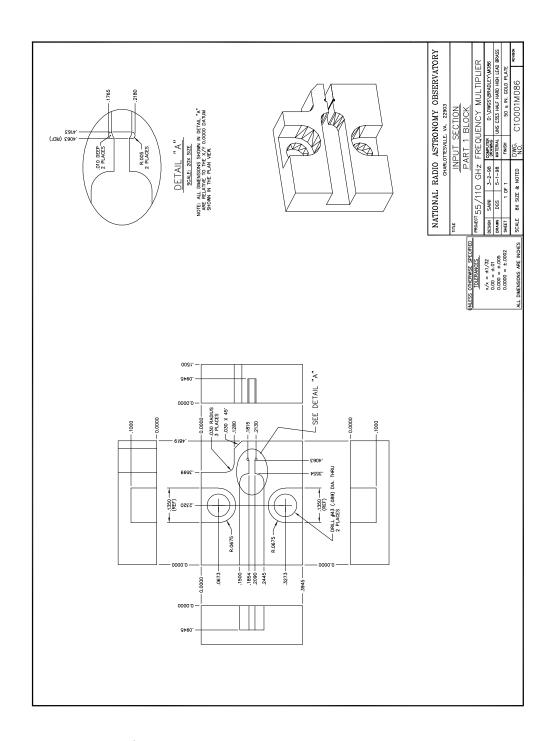

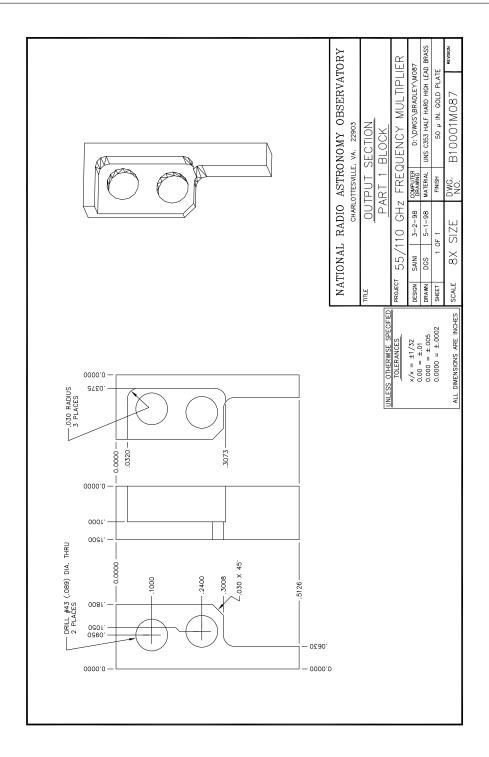

| D.2 | $55/110~\mathrm{GHz}$ frequency doubler: Internal mechanical assembly |

|     | of parts 1 and 2 of the split block                                   |

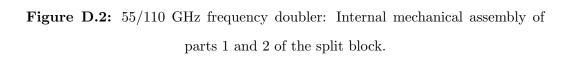

| D.3 | 55/110 GHz frequency doubler: External mechanical assembly            |

|     | of parts 1 and 2 of the split block                                   |

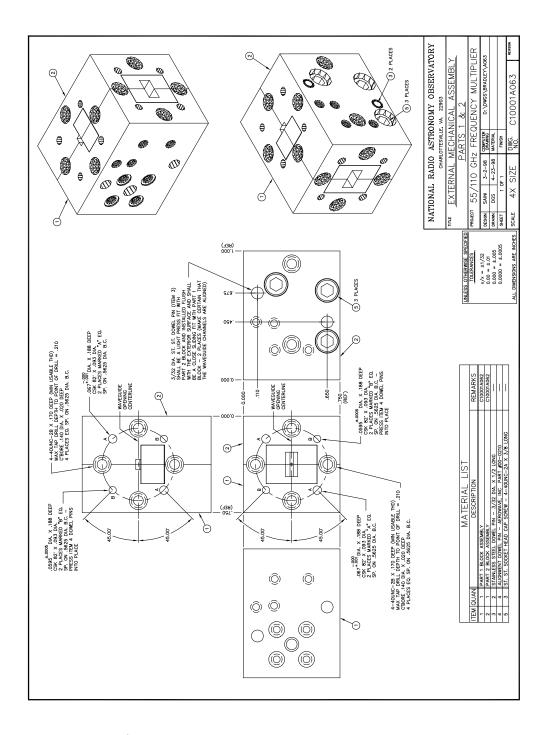

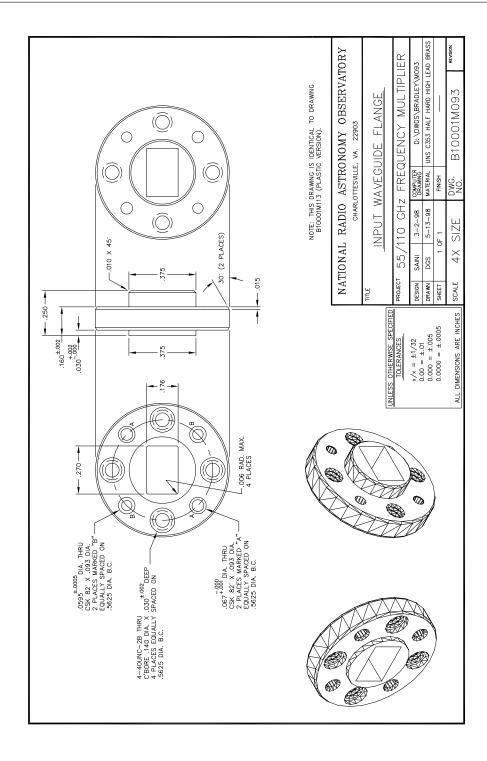

| D.4 | 55/110  GHz frequency doubler: WR-19 input waveguide flange           |

|     | adapter assembly                                                      |

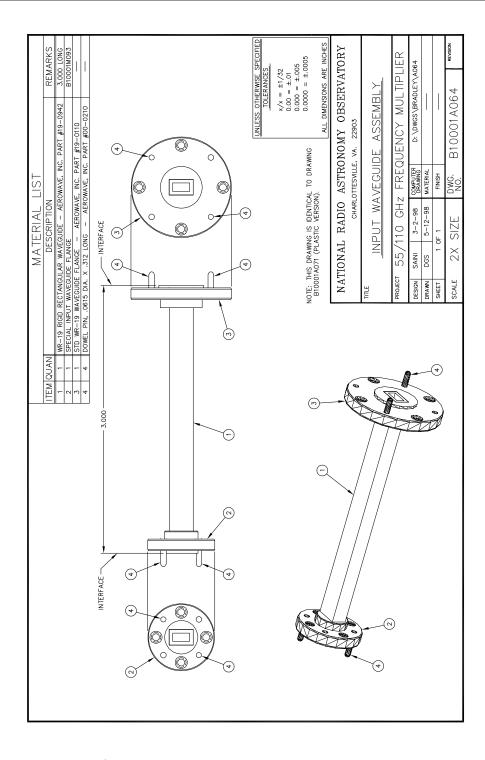

| D.5 | 55/110  GHz frequency doubler: WR-8 output waveguide flange           |

|     | adapter assembly                                                      |

| D.6 | 55/110 GHz frequency doubler: Mechanical details of part 1            |

|     | of the two piece split block                                          |

| D.7 $55/110$ GHz frequency doubler: Mechanical details of the in-             |

|-------------------------------------------------------------------------------|

| put section insert of part 1 of the two piece split block 218                 |

| D.8 $55/110$ GHz frequency doubler: Mechanical details of the out-            |

| put section insert of part 1 of the two piece split block 219                 |

| D.9 $55/110$ GHz frequency doubler: Mechanical details of part 2              |

| of the two piece split block                                                  |

| $\mathrm{D.10}\;55/110$ GHz frequency doubler: Mechanical details of the in-  |

| put section insert of part 2 of the two piece split block 221                 |

| D.11 55/110 GHz frequency doubler: Mechanical details of the out-             |

| put section insert of part 2 of the two piece split block 222                 |

| $\mathrm{D.12}\;55/110$ GHz frequency doubler: Location of the relief area in |

| one of the halves (part 2) of the two piece split block 223                   |

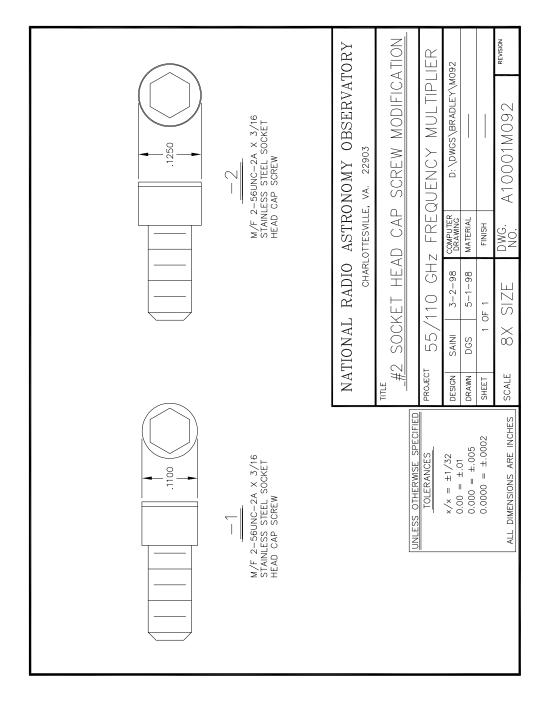

| $\rm D.13~55/110~GHz$ frequency doubler: Details of the modified socket       |

| screws used to secure the input and output inserts into the                   |

| two halves of the split block                                                 |

| $\rm D.14~55/110~GHz$ frequency doubler: Mechanical details of the spe-       |

| cial WR-19 input waveguide flange                                             |

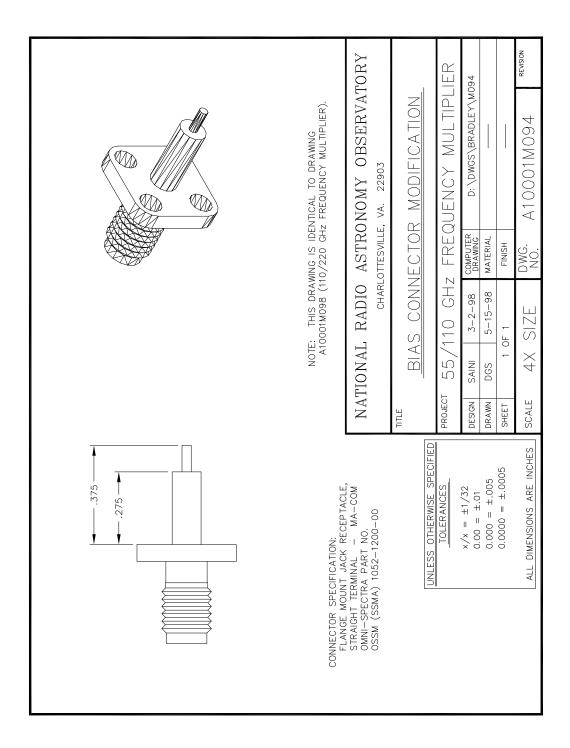

| $\rm D.15~55/110~GHz$ frequency doubler: Details of the modified SSMA         |

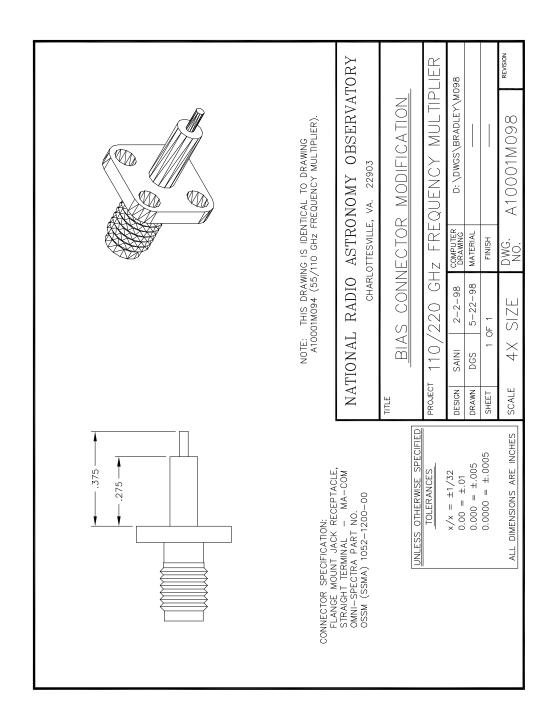

| flange mount jack receptacle used as the DC bias connector. $\ . \ 226$       |

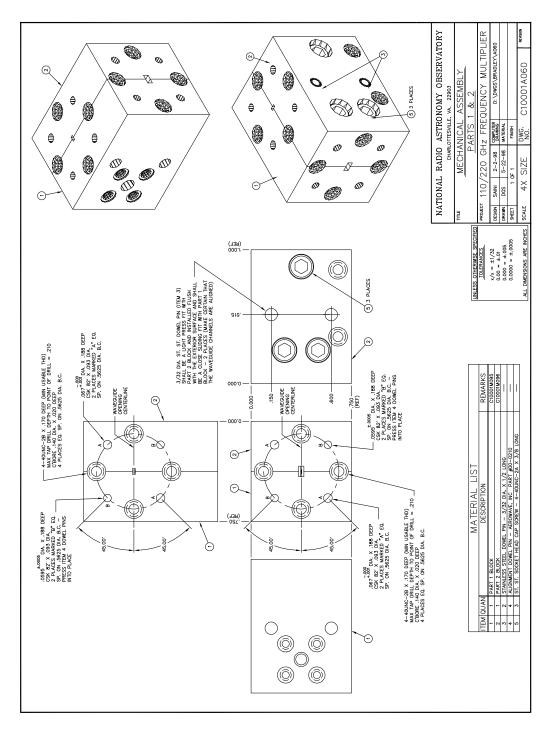

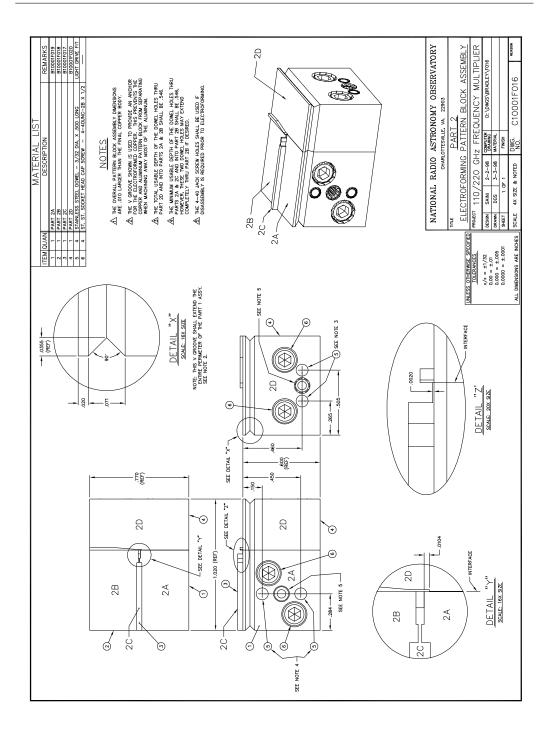

| $\mathrm{D.16}\ 110/220$ GHz frequency doubler: Mechanical assembly of the    |

| split block showing the DC bias connector and the waveguide                   |

| flange adapters                                                               |

| $\rm D.17\;110/220~GHz$ frequency doubler: External mechanical assem-         |

| bly of parts 1 and 2 of the split block                                       |

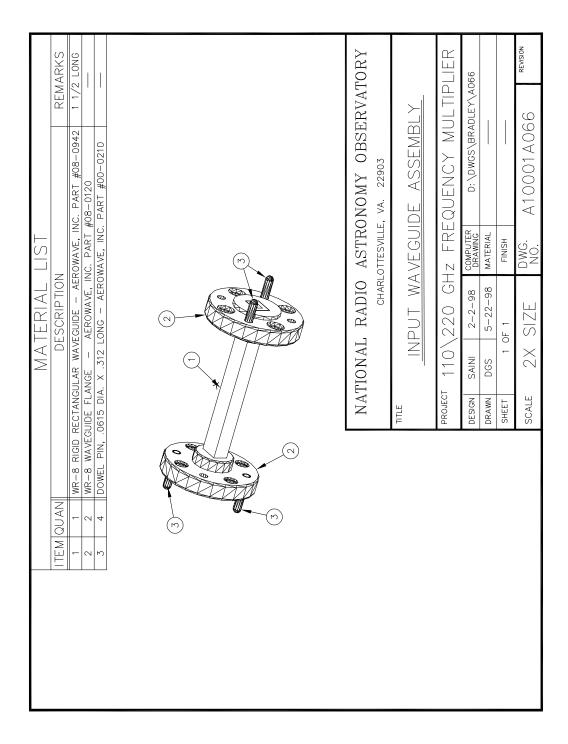

| D.18 110/220 GHz frequency doubler: WR-8 input waveguide flange $$          |

|-----------------------------------------------------------------------------|

| adapter assembly                                                            |

| D.19 $110/220~\mathrm{GHz}$ frequency doubler: WR-4 output waveguide flange |

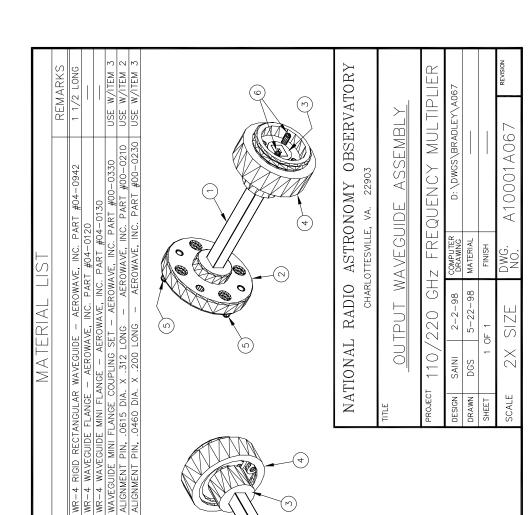

| adapter assembly                                                            |

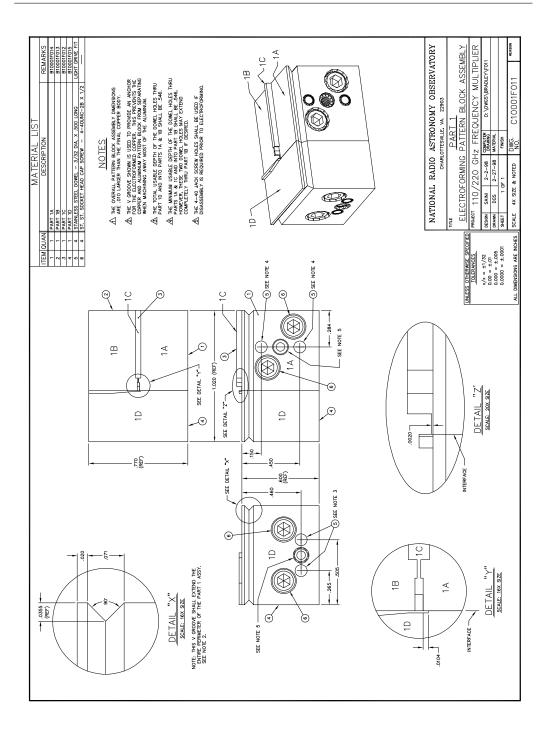

| $D.20 \ 110/220$ GHz frequency doubler: Assembly of the mandrel             |

| components 1A through 1D. This mandrel was used for elec-                   |

| troforming part 1 of the split block                                        |

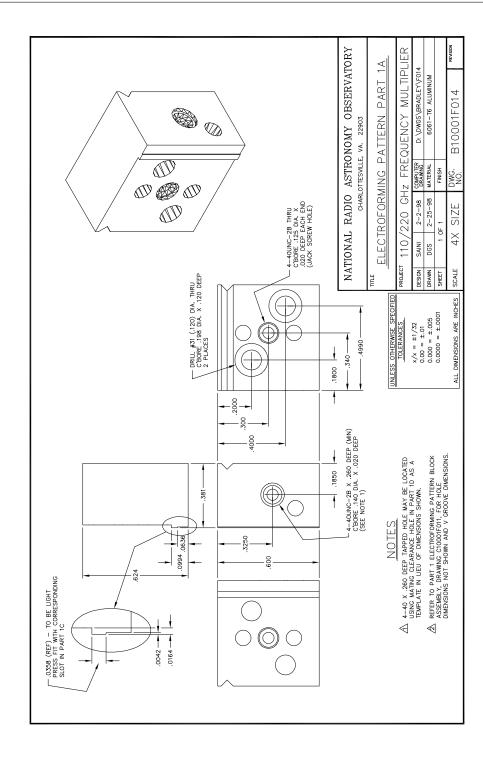

| $D.21 \ 110/220$ GHz frequency doubler: Mechanical details of the           |

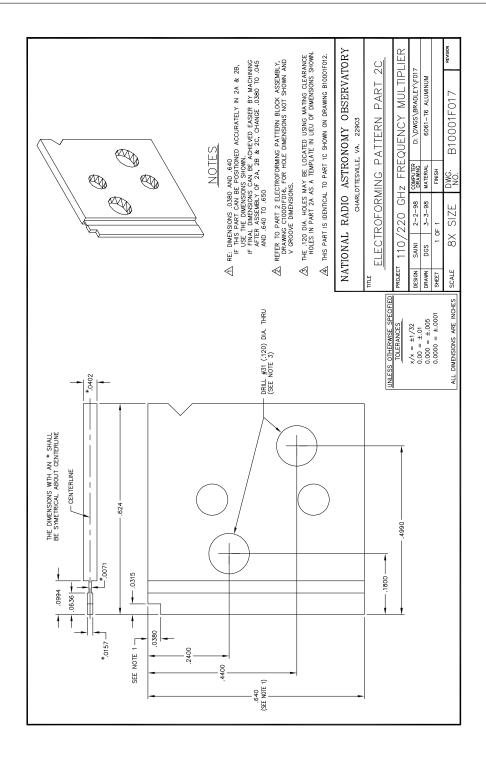

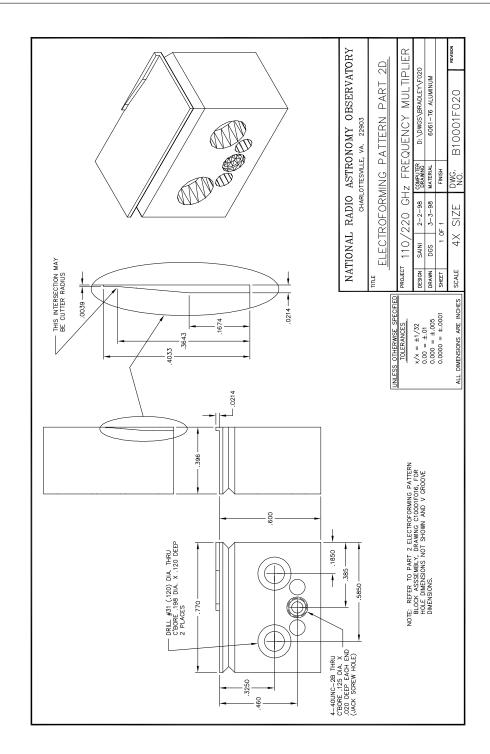

| mandrel part 1A                                                             |

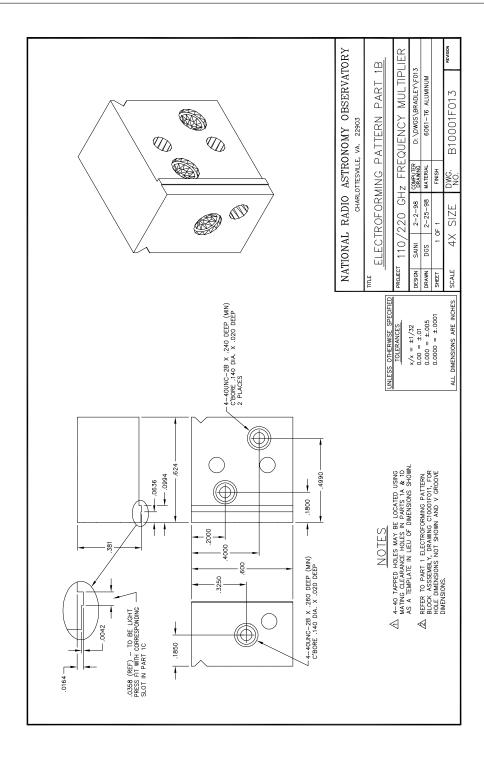

| $D.22 \ 110/220$ GHz frequency doubler: Mechanical details of the           |

| mandrel part 1B                                                             |

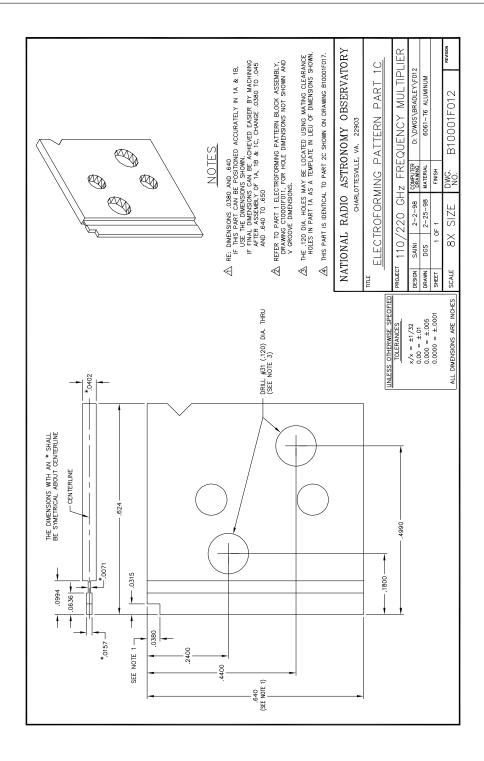

| $D.23 \ 110/220$ GHz frequency doubler: Mechanical details of the           |

| mandrel part 1C                                                             |

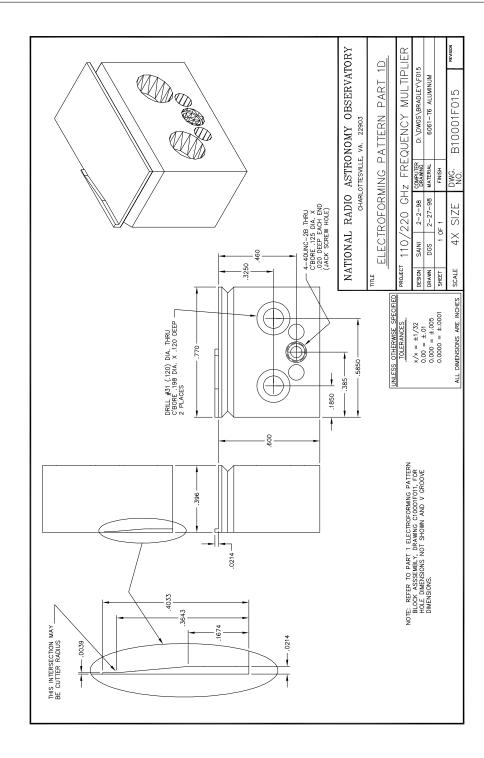

| $D.24 \ 110/220$ GHz frequency doubler: Mechanical details of the           |

| mandrel part 1D                                                             |

| $D.25 \ 110/220$ GHz frequency doubler: Assembly of the mandrel             |

| components 2A through 2D. This mandrel was used for elec-                   |

| troforming part 2 of the split block                                        |

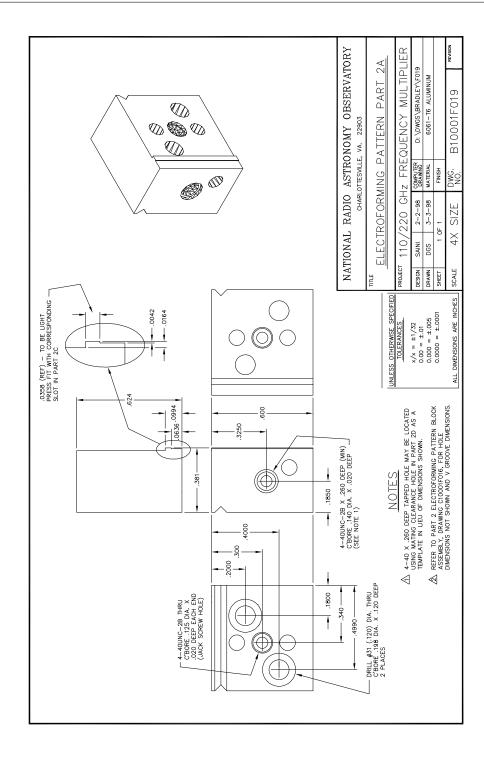

| D.26 110/220 GHz frequency doubler: Mechanical details of the               |

| mandrel part 2A                                                             |

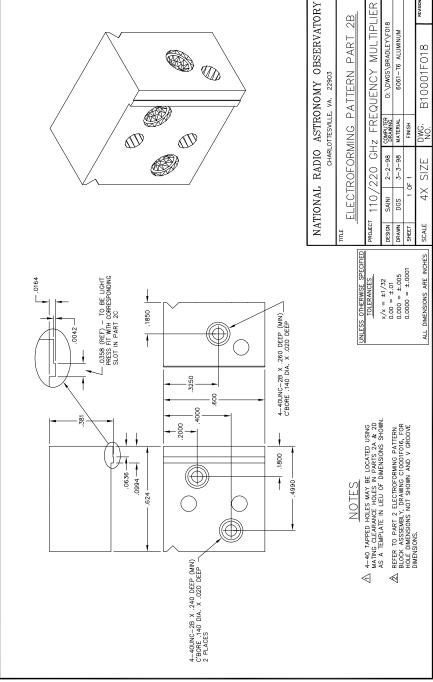

| $D.27 \ 110/220$ GHz frequency doubler: Mechanical details of the           |

| mandrel part 2B                                                             |

| D.28 110/220 GHz frequency doubler: Mechanical details of the               |

| mandrel part 2C                                                             |

| D.29 110/220 GHz frequency doubler: Mechanical details of the $$               |

|--------------------------------------------------------------------------------|

| mandrel part 2D                                                                |

| $D.30 \ 110/220$ GHz frequency doubler: Details of the machining               |

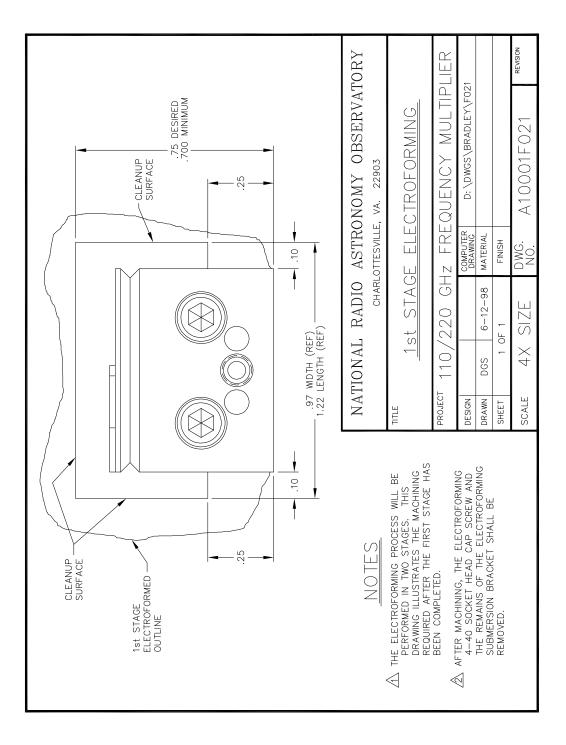

| needed after completion of the first stage of electroforming 241 $$            |

| D.31 110/220 GHz frequency doubler: Details of the machining                   |

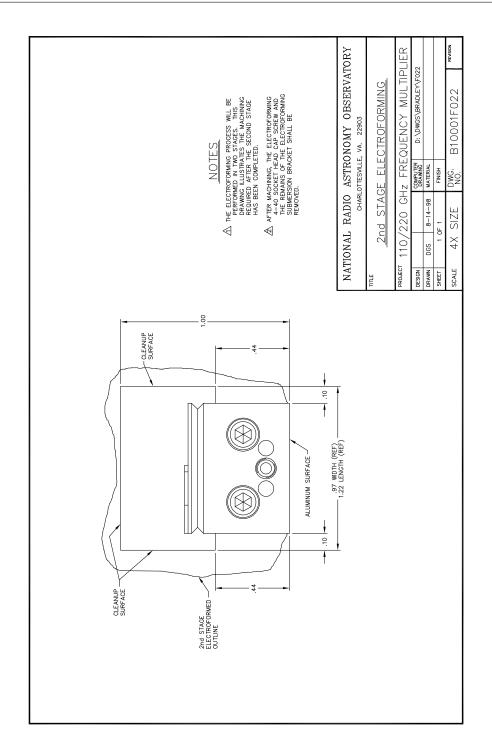

| needed after completion of the second and final stage of elec-                 |

| troforming                                                                     |

| $\mathrm{D.32}\;110/220$ GHz frequency doubler: Mechanical details of part 1   |

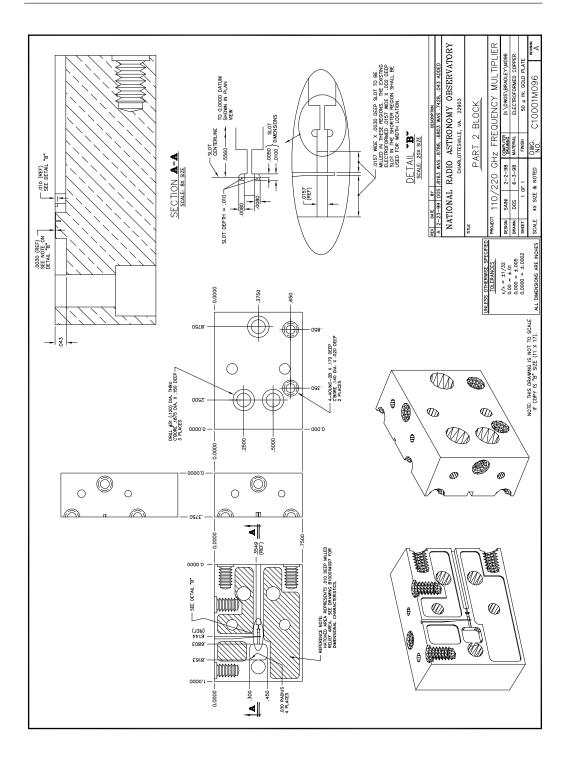

| of the two piece split block                                                   |

| D.33 $110/220~\mathrm{GHz}$ frequency doubler: Mechanical details of part 2    |

| of the two piece split block                                                   |

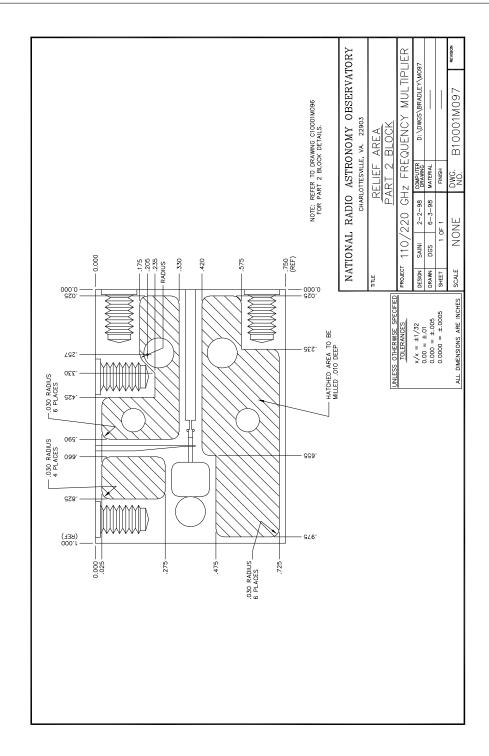

| $\mathrm{D.34}\;110/220$ GHz frequency doubler: Location of the relief area in |

| one of the halves (part 2) of the two piece split block 245                    |

| $\rm D.35~110/220~GHz$ frequency doubler: Details of the modified SSMA         |

| flange mount jack receptacle used as the DC bias connector. $\ . \ 246$        |

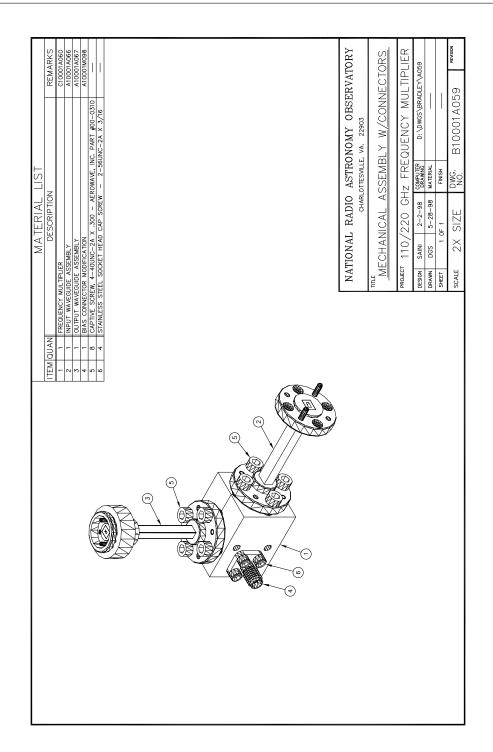

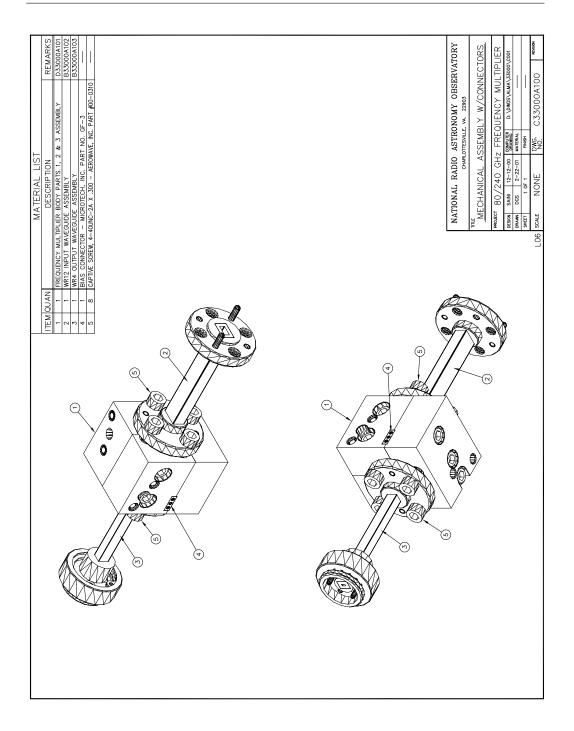

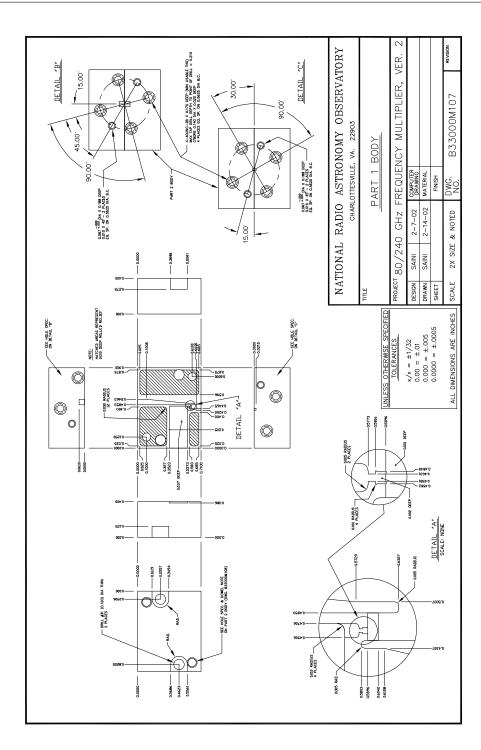

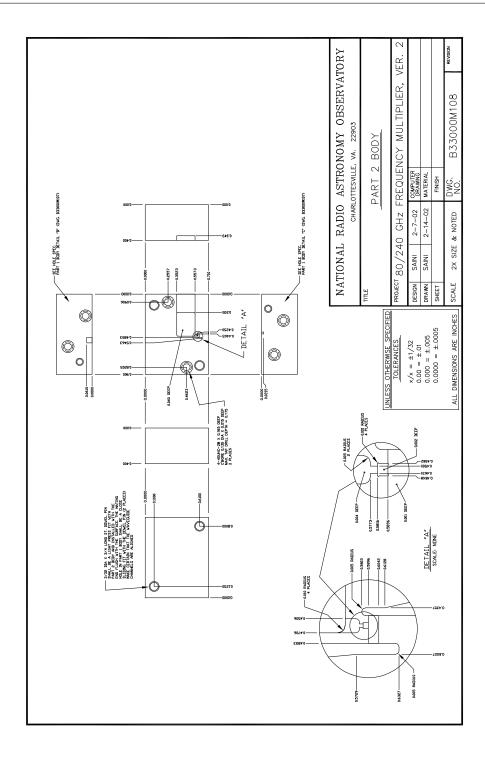

| $\rm D.36~80/240~GHz$ frequency tripler, version 1: Mechanical assembly        |

| of the three piece block showing the DC bias connector and                     |

| the waveguide flange adapters                                                  |

| $\rm D.37~80/240~GHz$ frequency tripler, version 1: External mechanical        |

| assembly of parts 1, 2 and 3 comprising the metal block 248 $$                 |

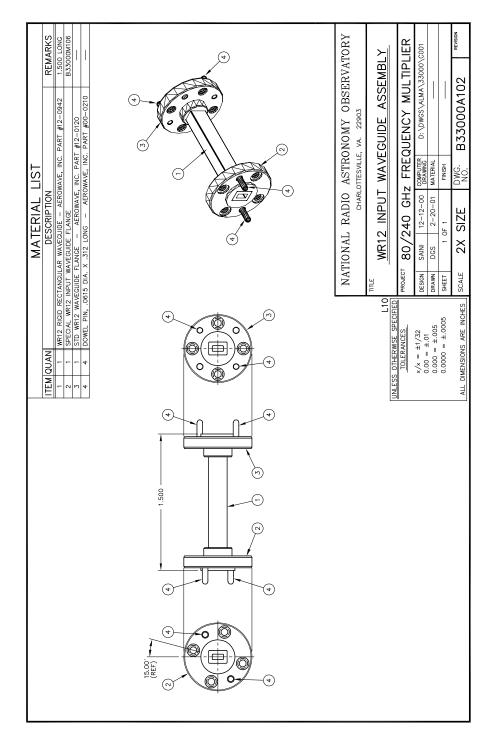

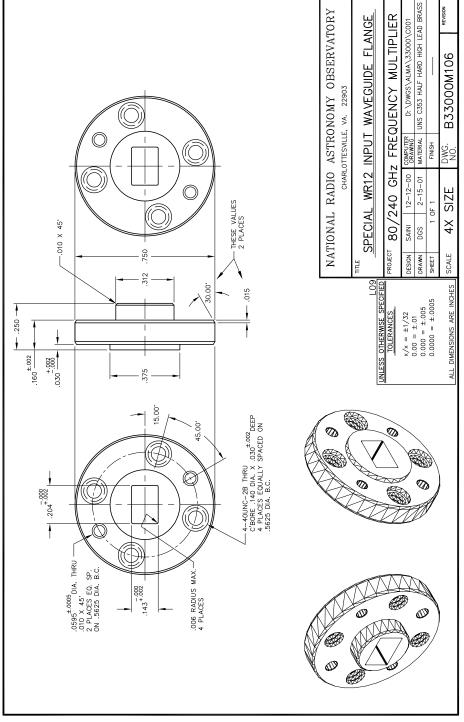

| D.38 80/240 GHz frequency tripler, version 1 and 2: WR-12 input                |

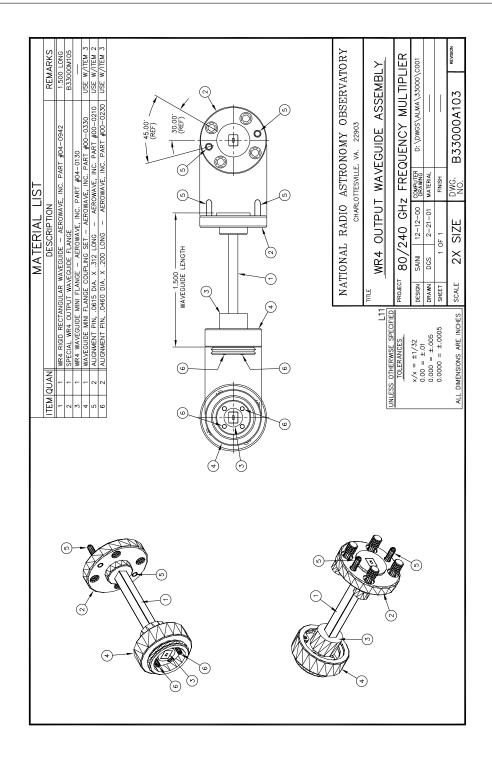

| waveguide flange adapter assembly                                              |

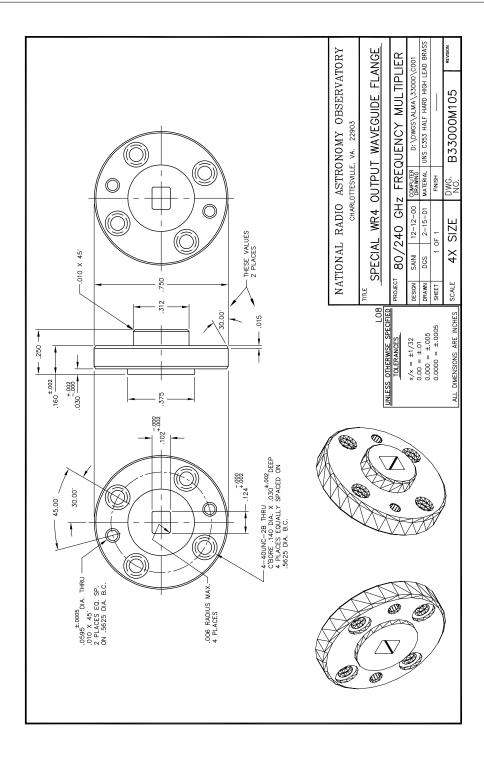

| $\rm D.39~80/240~GHz$ frequency tripler, version 1 and 2: WR-4 output          |

| waveguide flange adapter assembly                                              |

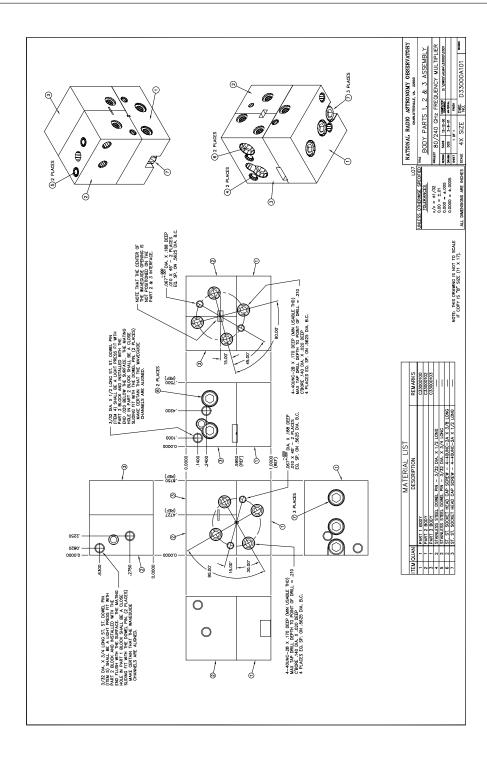

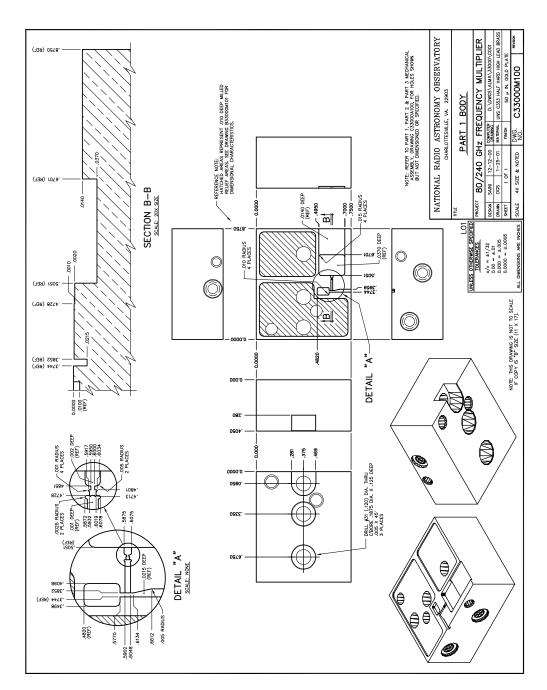

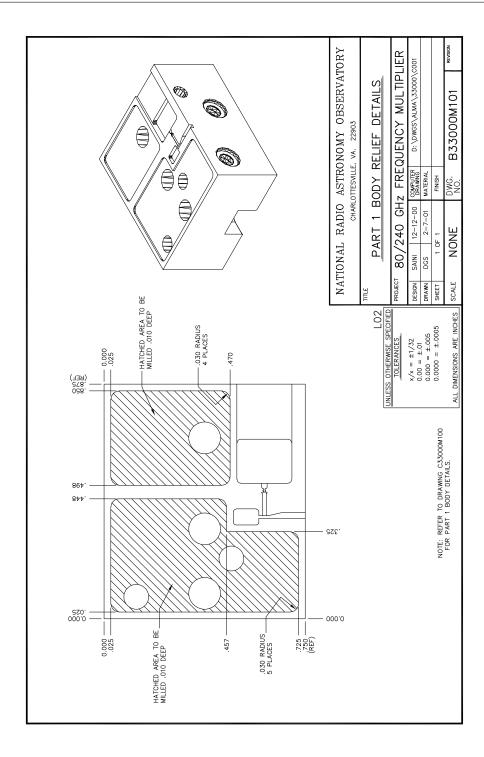

| $D.40\ 80/240$ GHz frequency tripler, version 1: Mechanical details        |   |

|----------------------------------------------------------------------------|---|

| of part 1 of the three piece metal block                                   | 1 |

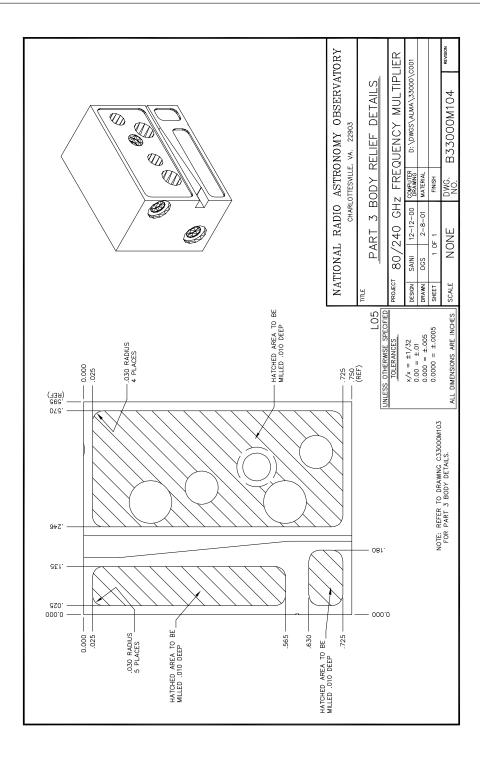

| $\rm D.41~80/240~GHz$ frequency tripler, version 1: Location of the relief |   |

| area in part 1 of the three piece metal block. $\ldots \ldots \ldots 255$  | 2 |

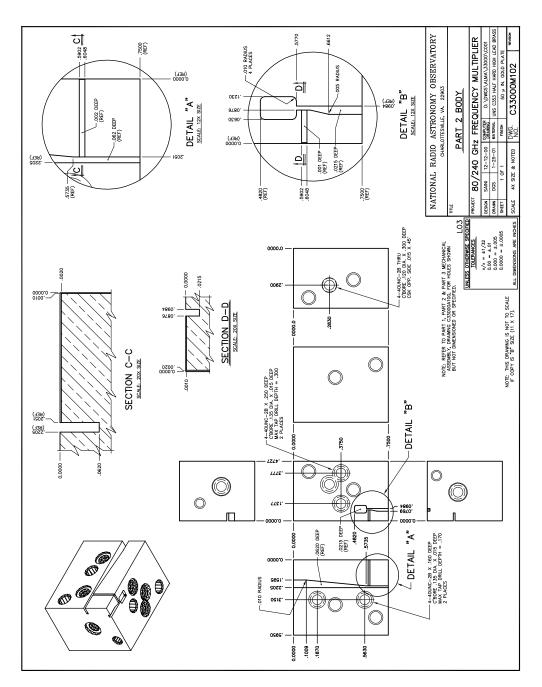

| D.42.80/240 GHz frequency tripler, version 1: Mechanical details           |   |

| of part 2 of the three piece metal block                                   | 3 |

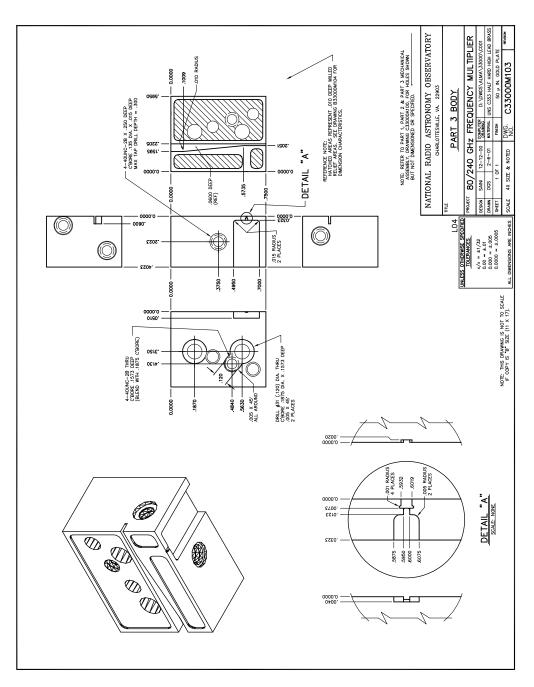

| D.43 80/240 GHz frequency tripler, version 1: Mechanical details           |   |

| of part 3 of the three piece metal block                                   | 4 |

| $\rm D.44~80/240~GHz$ frequency tripler, version 1: Location of the relief |   |

| area in part 3 of the three piece metal block. $\ldots \ldots \ldots 258$  | 5 |

| D.45 80/240 GHz frequency tripler, version 1 and 2: Mechanical             |   |

| details of the special WR-4 output waveguide flange 250 $$                 | 6 |

| $D.46\ 80/240\ GHz$ frequency tripler, version 1 and 2: Mechanical         |   |

| details of the special WR-12 input waveguide flange 25'                    | 7 |

| D.47 80/240 GHz frequency tripler, version 2: Mechanical details           |   |

| of part 1 of the two piece split block                                     | 8 |

| $D.48\ 80/240$ GHz frequency tripler, version 2: Mechanical details        |   |

| of part 2 of the two piece split block                                     | 9 |

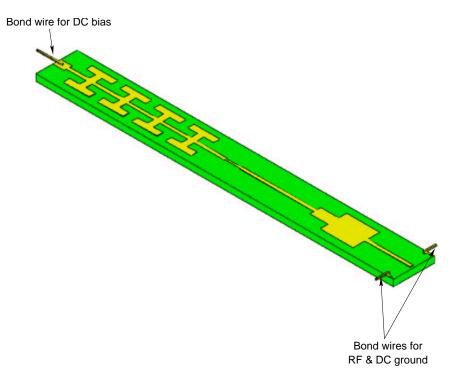

| E.1 Bond wire locations on the $55/110$ GHz frequency doubler              |   |

| quartz circuit.                                                            | 1 |

| -                                                                          | T |

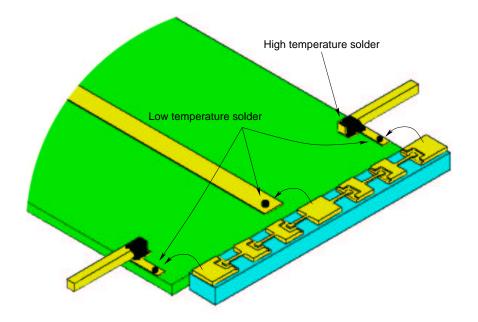

| E.2 Close up of the area that receives the diode array. The location       |   |

| of the spots with high and low temperature solder is marked.               |   |

| The diode is also shown placed near the location where it is               |   |

| to be attached                                                             | 3 |

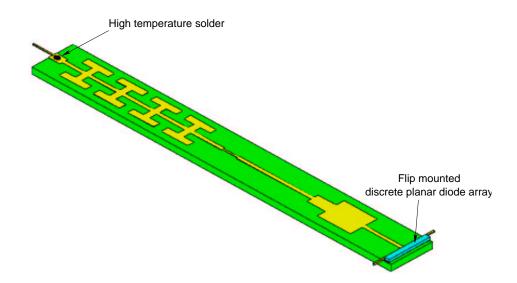

| E.3 | Diagram of the quartz circuit after completion of the assembly  |     |

|-----|-----------------------------------------------------------------|-----|

|     | procedure.                                                      | 264 |

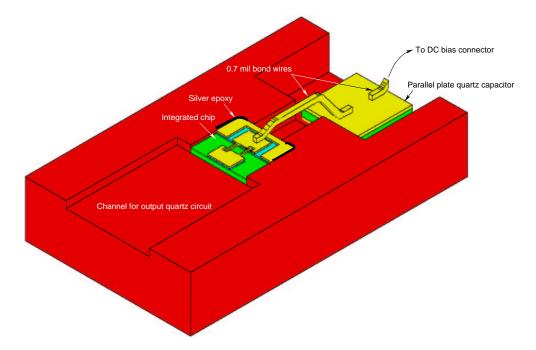

| E.4 | Cut away view of the metal housing showing the location of      |     |

|     | the DC bias quartz capacitor and the diode chip. The location   |     |

|     | of the epoxy used to connect the ground pads to the metal       |     |

|     | housing is shown. Also shown are the 0.7 mil bond wires used    |     |

|     | to supply the DC bias to the diode chip                         | 265 |

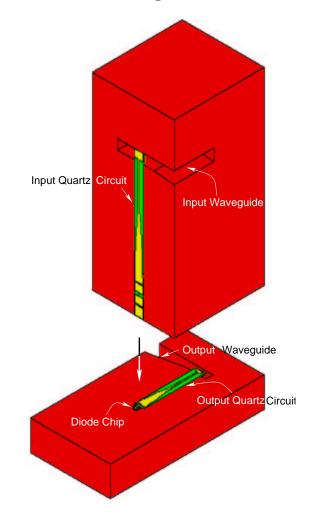

| E.5 | Cut away view of the relevant pieces of the metal housing       |     |

|     | showing the relative placement of the diode chip, the input     |     |

|     | quartz circuit and the output quartz circuit. The DC bias       |     |

|     | arrangement located adjacent to the diode chip is not shown     | 266 |

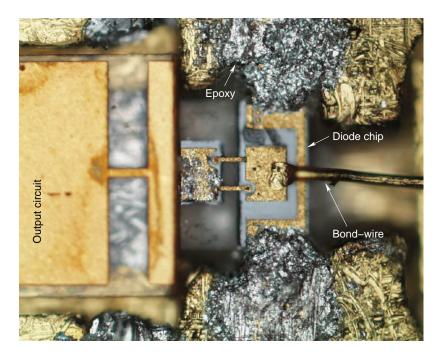

| E.6 | Photo of the metal block showing the diode chip and the out-    |     |

|     | put circuit. A portion of the bond wire used for supplying the  |     |

|     | DC bias to the chip can be seen. The location of silver epoxy   |     |

|     | used to ground the chip pads is marked                          | 267 |

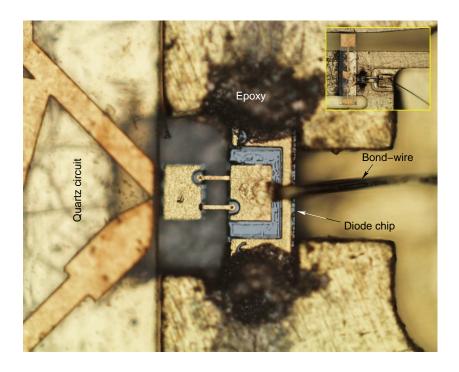

| E.7 | Photo of the metal block showing the diode chip and the         |     |

|     | quartz circuit. A portion of the bond wire used for supply-     |     |

|     | ing the DC bias to the chip can be seen. The location of silver |     |

|     | epoxy used to ground the chip pads is marked. Inset in the top  |     |

|     | right corner is an overall view of the block showing the entire |     |

|     | quartz circuit seated next to the diode chip. The quartz DC     |     |

|     | bias capacitor as well as the $0.7$ mil diameter bond wires can |     |

|     |                                                                 |     |

## List of Tables

| 3   |

|-----|

|     |

| 8   |

| 9   |

| 13  |

| 14  |

|     |

| 15  |

|     |

| 94  |

|     |

| 173 |

| 174 |

|     |

| 178 |

|     |

| 179 |

|     |

| A.5  | State-of-the-art frequency multiplier performance (Schottky       |

|------|-------------------------------------------------------------------|

|      | diode based)                                                      |

| A.6  | State-of-the-art frequency multiplier performance (Schottky       |

|      | diode based)                                                      |

| A.7  | State-of-the-art frequency multiplier performance (Other two-     |

|      | terminal device based)                                            |

| A.8  | State-of-the-art frequency multiplier performance (Other two-     |

|      | terminal device based)                                            |

| A.9  | State-of-the-art frequency multiplier performance (Three-terminal |

|      | device based)                                                     |

| A.10 | State-of-the-art frequency multiplier performance (Three-terminal |

|      | device based)                                                     |

| A.11 | State-of-the-art frequency multiplier performance (Three-terminal |

|      | device based)                                                     |

| A.12 | State-of-the-art frequency multiplier performance (Distributed    |

|      | element structures)                                               |

### List of Symbols

- A Contact area of a diode junction.

- $C_{fp}$  Finger to pad parasitic capacitance in a planar diode geometry.

- $C_{j0}$  Zero bias junction capacitance of a diode, equivalent to  $C_j(V_j = 0)$ .

- $C_j(V_j)$  Capacitance of a diode junction. (Function of the potential difference across the junction.)

- $C_{pp}$  Pad to pad parasitic capacitance in a planar diode geometry.

- E Electric field. (Exception : In Chapter 5, due to a lack of better notation, this symbol has been used to represent time dependant amplitude of a noisy input pump signal to a frequency multiplier.)

- I(t) Electric current. (Function of time.)

- $I_0$  Reverse saturation current of a Schottky junction or diode.

- $I_L(t)$  Current in the "load" termination. (Function of time.)

- $I_{max}$  Velocity saturation limited drift current.

- $I_n(t)$  Electric current. (Function of time.)

- $K_{\pm n,\pm 1}(f)$  Transmission coefficients relating the sidebands of the Fourier spectrum of the output voltage waveform of a frequency multiplier to the sidebands of the Fourier spectrum of the input voltage waveform. (Function of frequency.)

- $L_f$  Inductance of the bridge or finger metalization in a planar diode geometry.

- $N_{buffer}$  Doping concentration of the buffer layer in a diode.

- $N_d$  Doping concentration of the epitaxial layer in a diode.

- P Power.

- $P_{in}$  Available input pump power to a frequency multiplier.

- $P_{out}$  Available output power of a frequency multiplier.

- Q(V) Charge stored in a Schottky junction. (Function of electric potential difference across the junction.)

- $R_{buffer}$  Resistance of the buffer layer.

- $R_{epi}$  Resistance of the undepleted epitaxial layer.

- $R_j$  Parasitic (leakage) resistance of a diode junction.

- $R_{ohmic}$  Resistance of the ohmic contact between the buffer layer and the contact metalization for the terminal.

- $R_{spread}$  Spreading resistance to account for the ohmic losses arising in the buffer layer as the vertical column of current spreads out into the bulk of the buffer region.

- $R_s$  Total parasitic series resistance of a diode.

- $\mathbf{S}_{\mathbf{e}}(\mathbf{f})$  The noise power spectrum matrix of the input pump signal to a frequency multiplier.

- $S_e^{aa}(f)$  Element of the input power spectrum matrix, represents the amplitude noise spectrum of the signal.

- $S_e^{a\phi}(f)$  Element of the input power spectrum matrix, represents the cross correlation between the amplitude noise spectrum and the phase noise spectrum of the signal.

- $S_e^{\phi a}(f)$  Element of the input power spectrum matrix, represents the cross correlation between the phase noise spectrum and the amplitude noise spectrum of the signal.

- $S_e^{\phi\phi}(f)$  Element of the input power spectrum matrix, represents the phase noise spectrum of the signal.

- $S_{ij}$  Component of the S parameter matrix of a network representing a measure of the outgoing voltage wave amplitude at port – i due to an incident voltage wave at port – j.

- $\mathbf{S}_{\mathbf{v}}(\mathbf{f})$  The noise power spectrum matrix of the output signal from a frequency multiplier.

- $S_v^{aa}(f)$  Element of the output power spectrum matrix, represents the amplitude noise spectrum of the signal.

- $S_v^{a\phi}(f)$  Element of the output power spectrum matrix, represents the cross correlation between the amplitude noise spectrum and the phase noise spectrum of the signal.

- $S_v^{\phi a}(f)$  Element of the output power spectrum matrix, represents the cross correlation between the phase noise spectrum and the amplitude noise spectrum of the signal.

- $S_v^{\phi\phi}(f)$  Element of the output power spectrum matrix, represents the phase noise spectrum of the signal.

- $\mathbf{T}(\mathbf{f})$  The noise transmission matrix of a frequency multiplier. (Function of frequency.)

- $T_{aa}$  Element of the noise transmission matrix relating the output amplitude noise with the input amplitude noise.

- $T_{a\phi}(f)$  Element of the noise transmission matrix relating the output amplitude noise with the input phase noise. (Function of frequency.)

- $T_{\phi a}$  Element of the noise transmission matrix relating the output phase noise with the input amplitude noise.

- $T_{\phi\phi}(f)$  Element of the noise transmission matrix relating the output phase noise with the input phase noise. (Function of frequency.)

- V Electric potential or voltage. Also used to represent the amplitude of a voltage waveform.

- $V_{bi}$  Built in potential of a diode junction.

- $V_{br}$  Reverse breakdown voltage of a diode.

- $V_d$  Potential or voltage difference across the diode terminals.

- $V_j$  Potential or voltage difference across a diode junction.

- $V_s$  emf of a voltage source.

- Z Impedance.

- $Z_L$  Load impedance.

- $Z_{SHORT}\;$  Actual impedance of a practical short circuit.

- $Z_{emb}(f)$  Embedding impedance. (Function of frequency.)

- $Z_g$  Internal impedance of a voltage generator, used to drive a frequency multiplier.

- $Z_{idler}(f)$  Embedding impedance for the idler circuit of a frequency tripler. (Function of frequency.)

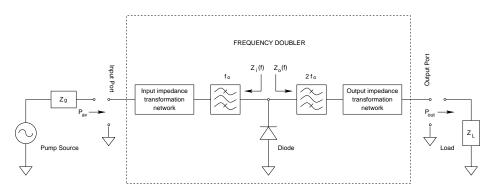

- $Z_i(f)$  Input embedding impedance. (Function of frequency.)

- $Z_o(f)$  Output embedding impedance. (Function of frequency.)

- $Z_{pi}$  Characteristic impedance of a transmission line structure calculated from the knowledge of power flowing through a given cross – section and the current distribution across it.

- $Z_{pv}$  Characteristic impedance of a transmission line structure calculated from the knowledge of power flowing through a given cross – section and the voltage distribution across it.

- $Z_{vi}$  Characteristic impedance of a transmission line structure calculated from the knowledge of current and voltage distribution across a given cross – section.

- $d_n$  Geometric lengths of features on a circuit layout.

- e Base of the natural logarithm, 2.71828182

- e(t) Instantaneous value of the voltage waveform of an input pump signal to a frequency multiplier.

- f Frequency.

- $f_0$  Frequency of the input pump signal to a frequency multiplier.

- k Boltzmann constant,  $1.380658 \times 10^{-23}$  J/K.

- n Multiplication order of a frequency multiplier. For instance, n = 2 for a frequency doubler etc.

- q Electronic charge,  $-1.60217733 \times 10^{-19}$  C.

- $r_a$  Radius of the junction contact, or "anode".

- $r_{oc}$  Inner radius of the ohmic contact.

- t Time.

- $t_{epi}$  Thickness of the epitaxial layer in a diode.

- $v_e$  Average electron drift velocity.

- $v_{sat}$  Average drift saturation velocity of electrons.

- $w(V_j)$  Width of the depletion region in a diode. (Function of the potential difference across the junction.)

- $\Delta \phi_c(t)$  Instantaneous phase noise in the waveform of the input pump signal to a frequency multiplier.

- $\Delta \varphi_v(t)$  Instantaneous phase noise in the waveform of the output signal from a frequency multiplier.

- $\Delta a_c(t)$  Instantaneous amplitude noise (fractional) in the input voltage waveform to a frequency multiplier.

- $\Delta a_v(t)$  Instantaneous amplitude noise (fractional) in the output voltage waveform from a frequency multiplier.

- $\Delta f_c(t)$  Instantaneous frequency deviation of a sinusiodal from its mean value, f<sub>0</sub>, due to phase fluctuations/noise.

- $\Gamma_{DUT}$  Reflection coefficient of a one port "device under test".

- $\Gamma_M$  Measured reflection coefficient of a circuit, at a particular port.

- $\delta A_c(f)$  Fourier transform of  $\Delta a_c(t)$ .

- $\delta A_v(f)$  Fourier transform of  $\Delta a_v(t)$ .

- $\delta E_l(f)$  Fourier spectrum (lower sideband) of the voltage waveform of the input pump signal to a frequency multiplier. (Function of frequency.)

- $\delta E_u(f)$  Fourier spectrum (upper sideband) of the voltage waveform of the input pump signal to a frequency multiplier. (Function of frequency.)

- $\delta V_l(f)$  Fourier spectrum (lower sideband) of the output voltage waveform of a frequency multiplier.

- $\delta V_u(f)$  Fourier spectrum (upper sideband) of the output voltage waveform of a frequency multiplier.

- $\delta_{buffer}$  Skin depth in the buffer layer of a diode.

- $\delta \Phi_c(f)$  Fourier transform of  $\Delta \phi_c(t)$ .

- $\delta \Phi_v(f)$  Fourier transform of  $\Delta \varphi_v(t)$ .

- $\epsilon_s$  Dielectric permittivity of GaAs, 13.1.

- $\gamma$  (V<sub>j</sub>) Correction factor used to account for the additional capacitance arising due to the fringing fields at the periphery of a Schottky junction. (Function of the potential difference across the junction.)

- $\mu_e$  Electron mobility in a semiconductor.

- $\mu_{epi}$  Electron mobility in n doped epitaxial layer.

- $\omega$  Radial frequency, equivalent to  $2\pi f$ .

- $\omega_0$  Radial frequency of the input pump signal to a frequency multiplier, equivalent to  $2\pi f_0$ .

- $\phi$  Phase.

- $\phi_c$  Initial phase of the voltage waveform of an input pump signal. to a frequency multiplier.

- $\phi_v$  Nonlinear phase term in the output voltage waveform of a frequency multiplier.

- $\pi$  3.141592654

- $\sigma_{buffer}$  Conductivity of the buffer layer in a diode.

- $\sigma_{epi}$  ~ Conductivity of the epitaxial layer in a diode.

- $\varphi_v$  Total phase of the voltage waveform at the output of a frequency multiplier.

### Chapter 1

## Introduction

Many physical phenomena can be studied through the measurement of electro-magnetic emissions in the millimeter and submillimeter part of the frequency spectrum. The observation technique employed can be passive whereby the naturally present emissions are simply measured, or active where the target is first illuminated by an appropriate wavelength radiation, and the reflected or transmitted energy is subsequently analyzed.

Applications of the passive technique include, but are not limited to, remote-sensing of the earth's surface from space-based and air-borne platforms, molecular spectroscopy and radio-astronomy. Remote-sensing can be employed to prospect for minerals, estimate the forest and crop cover, study weather patterns and track climatological changes. Most of these applications revolve around radiometric detection of certain target molecular energy-state transitions, which are in turn related to either emission or absorption lines in the millimeter and sub-millimeter part of the electro-magnetic spectrum. In radio-astronomy, the study of this subtly "encoded" information has revealed, and continues to uncover, vast amounts of knowledge about the formation and evolution of galaxies as well as the compositions of various stars and planets. The past of the universe can be actually "observed" by analyzing the radiation emitted a long time ago (at appropriate red-shifts).

Examples of the active technique can be found in automotive anti-collision systems, in the detection of concealed weapons, in airborne bio-chemical agent detection, in the detection of buried objects, in non-invasive materials testing, in aircraft instrument-landing systems, and in medical imaging. A significant application of the active imaging technique is also found in the estimation of radar cross-sections of various objects via illumination of their (reduced-size) scale models by a submillimeter-wave radar and subsequent measurement of the reflected energy.

### 1.1 Background and Motivation

The millimeter- and submillimeter-wave radio receivers are predominantly of two types: Direct detector type (like the bolometer) which are useful for applications requiring total power detection, and super-heterodyne type wherein the received radiation is down converted into an intermediate frequency (IF) signal for coherent detection and/or subsequent signal processing. Coherent detection is required for high resolution spectroscopy and radio interferometry. A key requirement for the operation of such a superheterodyne receiver is the availability of a local oscillator (LO) signal used to pump a non-linear component such as a low noise superconductor-insulatorsuperconductor (SIS) junction, a Schottky-diode, or a Hot Electron Bolometer (HEB) device, that down-converts the received signal while preserving its "information" bearing characteristics.

Table-1.1 lists the LO requirements of two millimeter- and submillimeterwave instruments currently under development: The very high resolution heterodyne spectrometer in a superfluid helium cryostat (HIFI) for the Herschel Space Observatory (HSO) satellite and the ground based Atacama Large Millimeter Array (ALMA) telescope.

| Project | LO Tuning Range | Mixer   | Required        | Notes                  | Reference |

|---------|-----------------|---------|-----------------|------------------------|-----------|

|         | (GHz)           | Element | LO Power        |                        |           |

| HSO     | 488 - 546       | SIS     | 25 - 50 $\mu W$ | The need for space-    | [1]       |

|         | 560 - 633       | &       |                 | qualification requires |           |

|         | 647 - 710       | HEB     |                 | extremely reliable,    |           |

|         | 724 - 793       |         |                 | very rugged, compact   |           |

|         | 807 - 848       |         |                 | & light-weight design  |           |

|         | 862 - 953       |         |                 |                        |           |

|         | 967 - 1042      |         |                 |                        |           |

|         | 1056 - 1113     |         |                 |                        |           |

|         | 1127 - 1178     |         |                 |                        |           |

|         | 1192 - 1242     |         |                 |                        |           |

| ALMA    | 27.3 - 33       | HFET    | $100 \ \mu W$   | Array configuration    | [2]       |

|         | 79 - 94         | &       |                 | requires a large       |           |

|         | 101 - 104       | SIS     | 15  mW (for     | number of sources.     |           |

|         | 137 - 151       |         | the first       | This implies that the  |           |

|         | 175 - 199       |         | two lower       | components should be   |           |

|         | 223 - 263       |         | bands with      | low-cost, moderately   |           |

|         | 287 - 358       |         | HFET-type       | reliable, compact &    |           |

|         | 397 - 488       |         | mixers)         | easily reproduceable.  |           |

|         | 614 - 708       |         |                 | LO should be remotely  |           |

|         | 799 - 938       |         |                 | tunable.               |           |

Table 1.1: Typical millimeter- and submillimeter-wave LO requirements.

For space-borne applications, the LO system needs to be extremely reliable since there is little possibility of carrying out any repairs subsequent to the launch of the instrument. Other desirable features include low power consumption, a light weight design, and compact size. Since only a few units need to be produced, cost and ease of assembly are secondary factors. However, for an earth based array telescope receiver, cost and reproduceability are important factors since large numbers of LO systems need to be manufactured. Although the systems are accessible for repairs after commissioning in this case, reliability of the LO system is critical to ensure low "down" times for the telescope considering the large number of LO systems that are deployed.

In the subsequent sections of this chapter, a survey of the existing millimeterand submillimeter-wave source technology is presented. The fundamental oscillator sources are reviewed first, followed by a brief summary of the current state-of-the-art of millimeter- and submillimeter-wave generation via photonic mixing and generation. The final part of the survey presents a comprehensive review of published literature on frequency multipliers spanning the past decade.

## 1.2 Fundamental Millimeter- and Submillimeterwave Oscillators

The fundamental millimeter- and submillimeter-wave oscillators may be classified as either tube-type (vacuum or gas-filled) or as solid-state devices. A comprehensive review of the available fundamental oscillator technologies can be found in [3] [4]. An overview of these technologies is presented on the following pages, together with some recent devlopments.

#### **1.2.1** Vacuum and Gas-filled Tube Sources

The most notable sources in this category are the Backward Wave Oscillator (BWO, also known by its trade name: Carcinotron), the Gyrotron, the Traveling Wave Tube Amplifier based oscillator (TWT), the Ledatron (Orotron) and the Magnetron.

Besides being based on "bulky" tubes, all of the above technologies require heavy and bulky support equipment (power supplies, and cooling equipment in some cases) which is an impediment to their use and acceptance. The reliability of vacuum tubes is itself somewhat questionable since the electron gun cathode filament slowly "evaporates" limiting the operational life of the tube. Furthermore, in most cases, the frequency of oscillation is determined by the size of the cavity or the length of the tube. Therefore, frequency tuning of these devices requires some kind of mechanical arrangement to change the size of the resonant cavity. Use of these oscillators as sources for high frequency LO is limited because it is difficult to suitably scale the mechanical structures for such operation.

Nevertheless there is a report of a BWO operating up to 1.2 THz (with 30% tuning band-width, and delivering 1 mW CW RF power) and a Ledatron source generating LO power up to several THz [4].

Although tube-based sources have found widespread application in the laboratory and on air-borne platforms, the weight, size and reliability issues mentioned earlier, have restricted the use of this technology for space applications. Being expensive, this technology is not very suitable for array type receivers either. Consequently, advances in tube technology appear to have leveled off and new sources incorporating tubes are relatively few in number.